USB on-the-go full-speed/high-speed (OTG_FS/OTG_HS) RM0390

1110/1328 RM0390 Rev 4

Data FIFO (DFIFO) access register map

These registers, available in both host and device modes, are used to read or write the FIFO

space for a specific endpoint or a channel, in a given direction. If a host channel is of type

IN, the FIFO can only be read on the channel. Similarly, if a host channel is of type OUT, the

FIFO can only be written on the channel.

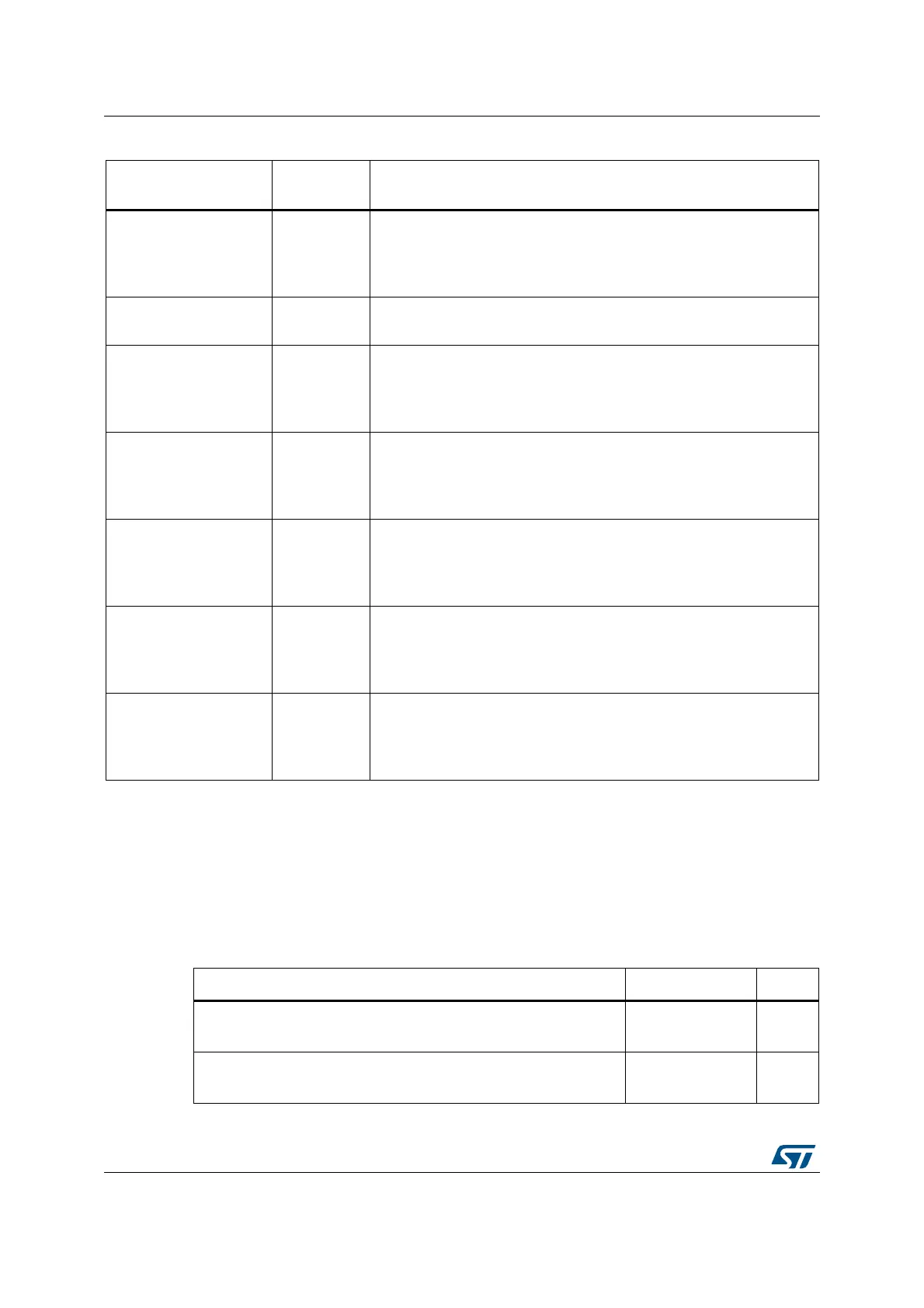

OTG_DOEPINTx

0xB08

0XB28

...

0xC08

Section 31.15.55: OTG device OUT endpoint x interrupt register

(OTG_DOEPINTx) (x = 0..5[FS] /8[HS], where x = Endpoint number)

for USB_OTG HS

OTG_DOEPTSIZ0 0xB10

Section 31.15.56: OTG device OUT endpoint 0 transfer size register

(OTG_DOEPTSIZ0)

OTG_DOEPDMAx

0xB14

0xB34

...

0xC14

Section 31.15.57: OTG device OUT endpoint x DMA address register

(OTG_DOEPDMAx) (x = 0..8, where x = endpoint number)

OTG_DOEPCTLx

0xB20

0xB40

...

0xBA0

Section 31.15.58: OTG device OUT endpoint x control register

(OTG_DOEPCTLx) (x = 1..5[FS] /8[HS], where x = endpoint number)

for USB_OTG FS

OTG_DOEPCTLx

0xB20

0xB40

...

0xC00

Section 31.15.58: OTG device OUT endpoint x control register

(OTG_DOEPCTLx) (x = 1..5[FS] /8[HS], where x = endpoint number)

for USB_OTG HS

OTG_DOEPTSIZx

0xB30

0xB50

...

0xBB0

Section 31.15.59: OTG device OUT endpoint x transfer size register

(OTG_DOEPTSIZx) (x = 1..5[FS] /8[HS], where x = Endpoint number)

for USB_OTG FS

OTG_DOEPTSIZx

0xB30

0xB50

..

0xBF0

Section 31.15.59: OTG device OUT endpoint x transfer size register

(OTG_DOEPTSIZx) (x = 1..5[FS] /8[HS], where x = Endpoint number)

for USB_OTG HS

Table 225. Device-mode control and status registers (continued)

Acronym

Offset

address

Register name

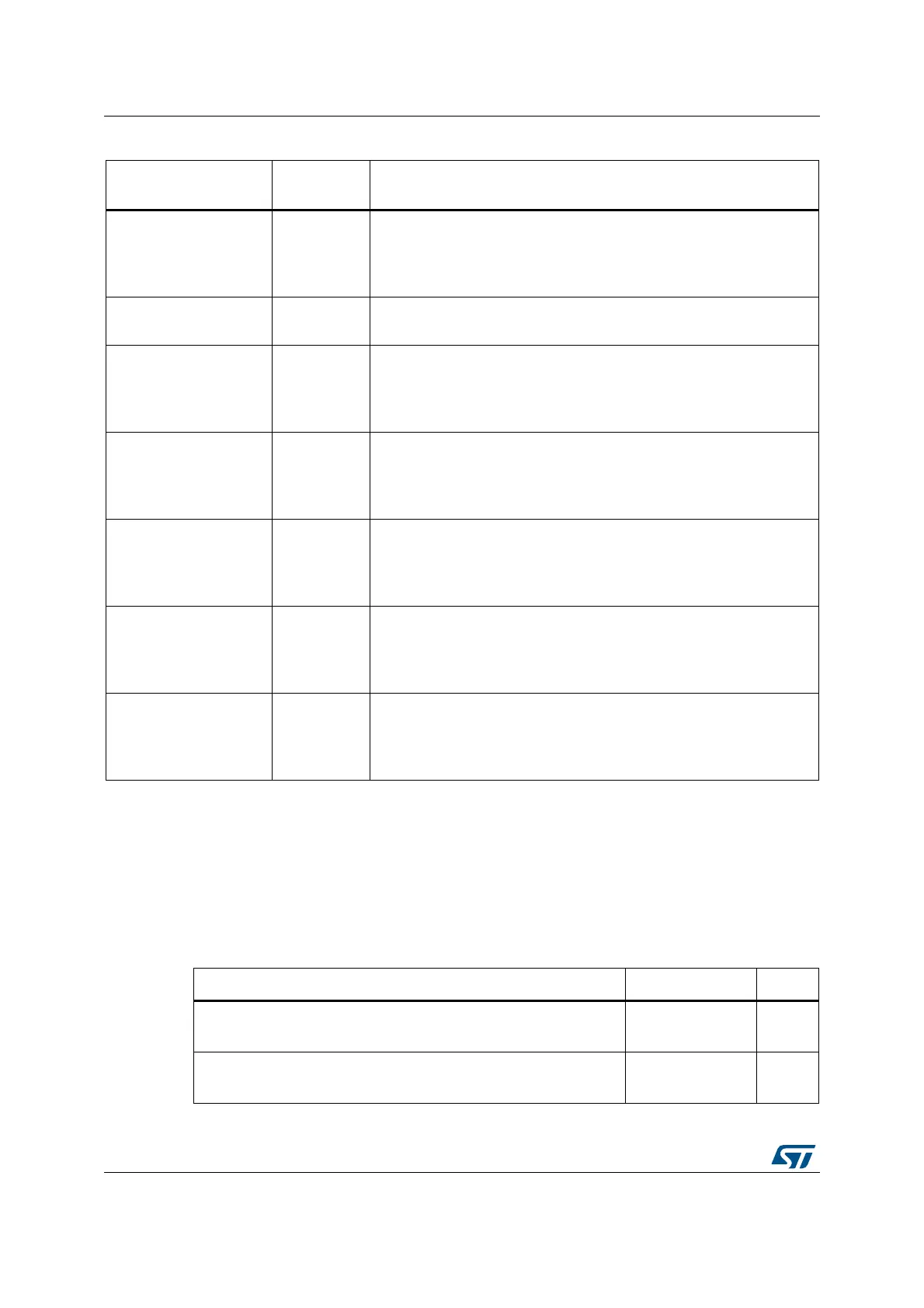

Table 226. Data FIFO (DFIFO) access register map

FIFO access register section Offset address Access

Device IN endpoint 0/Host OUT Channel 0: DFIFO write access

Device OUT endpoint 0/Host IN Channel 0: DFIFO read access

0x1000–0x1FFC

w

r

Device IN endpoint 1/Host OUT Channel 1: DFIFO write access

Device OUT endpoint 1/Host IN Channel 1: DFIFO read access

0x2000–0x2FFC

w

r

Loading...

Loading...