General-purpose timers (TIM9 to TIM14) RM0390

606/1328 RM0390 Rev 4

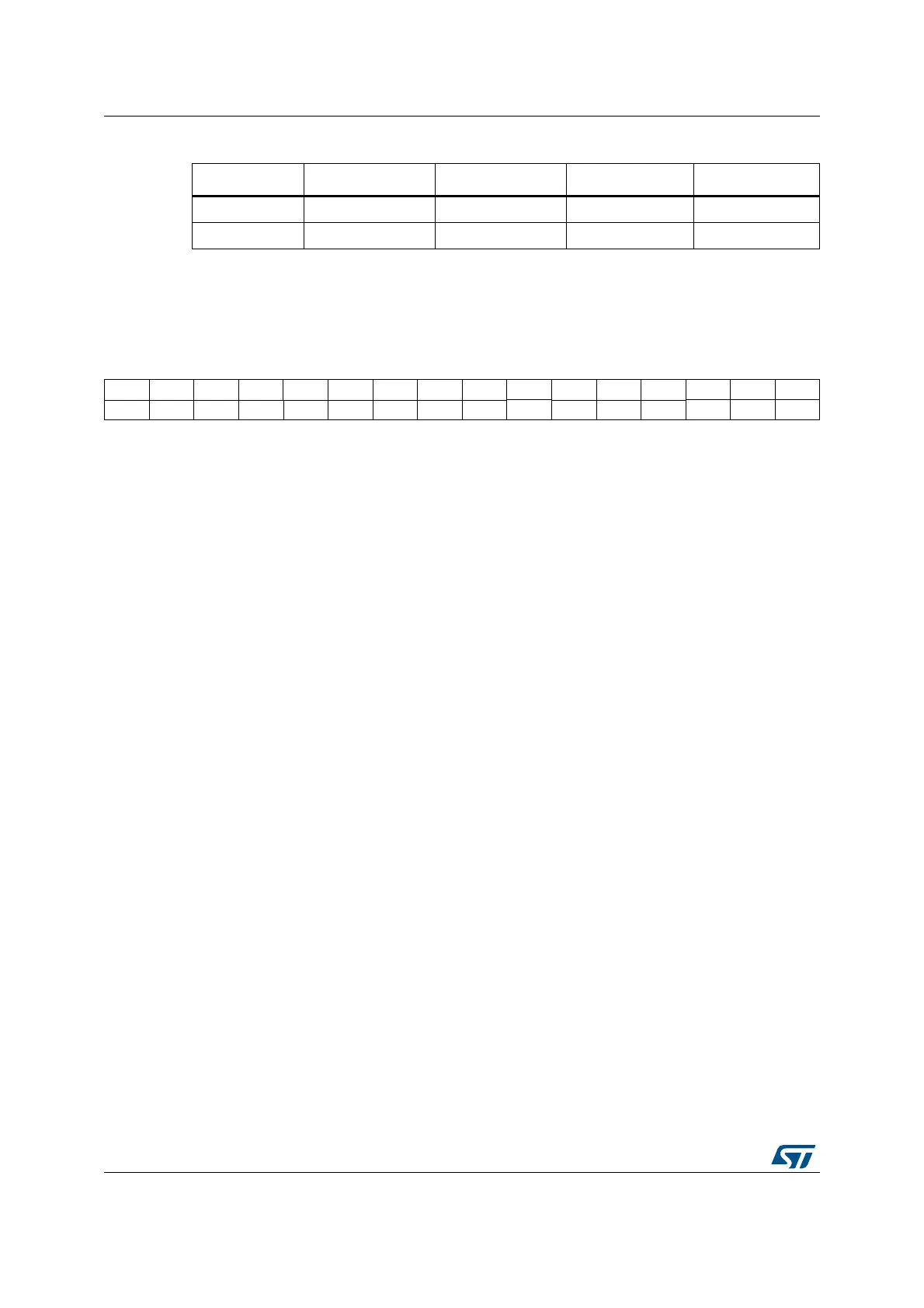

18.4.3 TIM9/12 Interrupt enable register (TIMx_DIER)

Address offset: 0x0C

Reset value: 0x0000

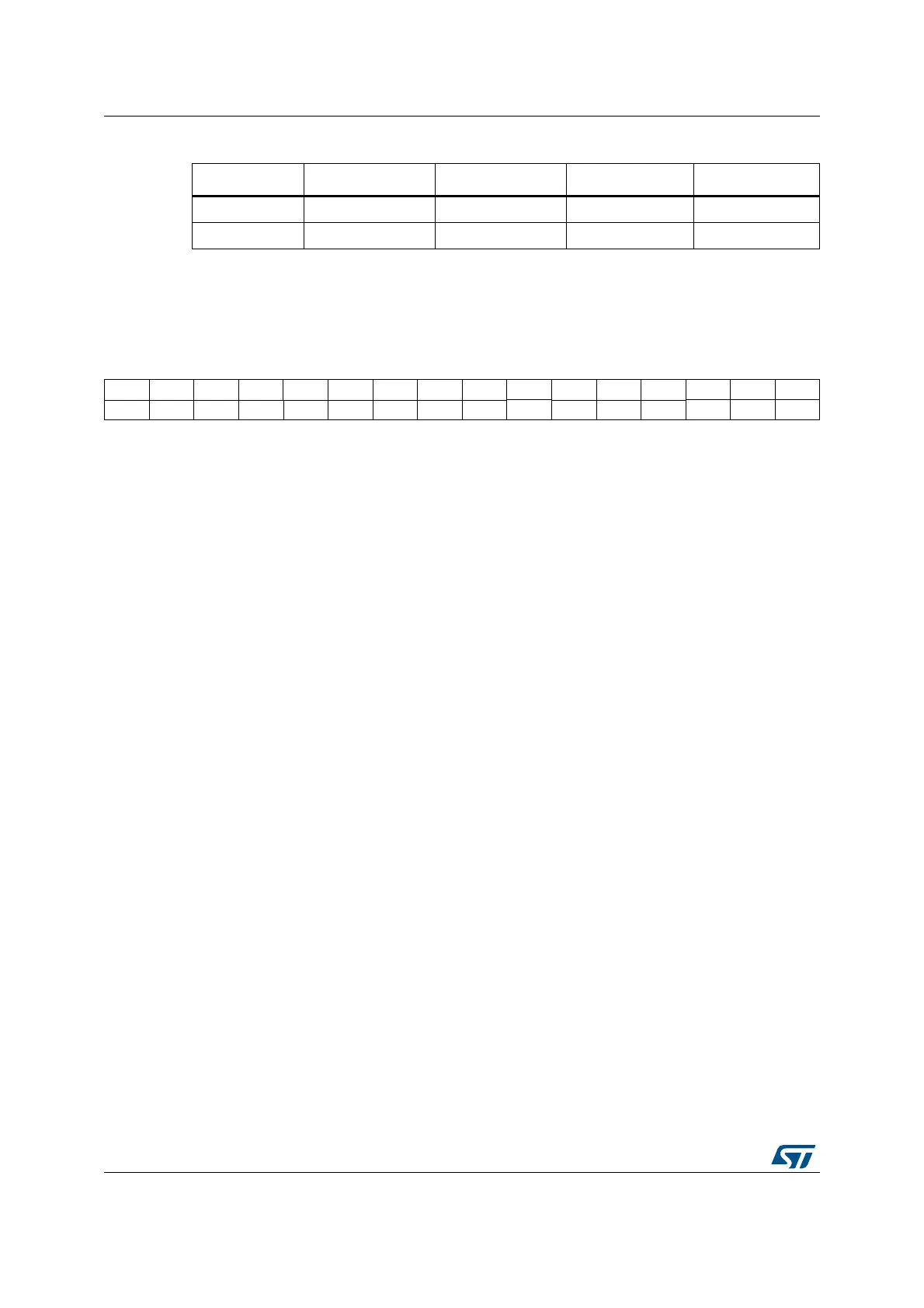

Table 115. TIMx internal trigger connections

Slave TIM ITR0 (TS = ‘000’) ITR1 (TS = ‘001’) ITR2 (TS = ‘010’) ITR3 (TS = ‘011’)

TIM9 TIM2 TIM3 TIM10_OC TIM11_OC

TIM12 TIM4 TIM5 TIM13_OC TIM14_OC

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. TIE Res. Res. Res. CC2IE CC1IE UIE

rw rw rw rw

Bits 15:7 Reserved, must be kept at reset value.

Bit 6 TIE: Trigger interrupt enable

0: Trigger interrupt disabled.

1: Trigger interrupt enabled.

Bits 5:3 Reserved, must be kept at reset value.

Bit 2 CC2IE: Capture/Compare 2 interrupt enable

0: CC2 interrupt disabled.

1: CC2 interrupt enabled.

Bit 1 CC1IE: Capture/Compare 1 interrupt enable

0: CC1 interrupt disabled.

1: CC1 interrupt enabled.

Bit 0 UIE: Update interrupt enable

0: Update interrupt disabled.

1: Update interrupt enabled.

Loading...

Loading...