RM0390 Rev 4 1153/1328

RM0390 USB on-the-go full-speed/high-speed (OTG_FS/OTG_HS)

1264

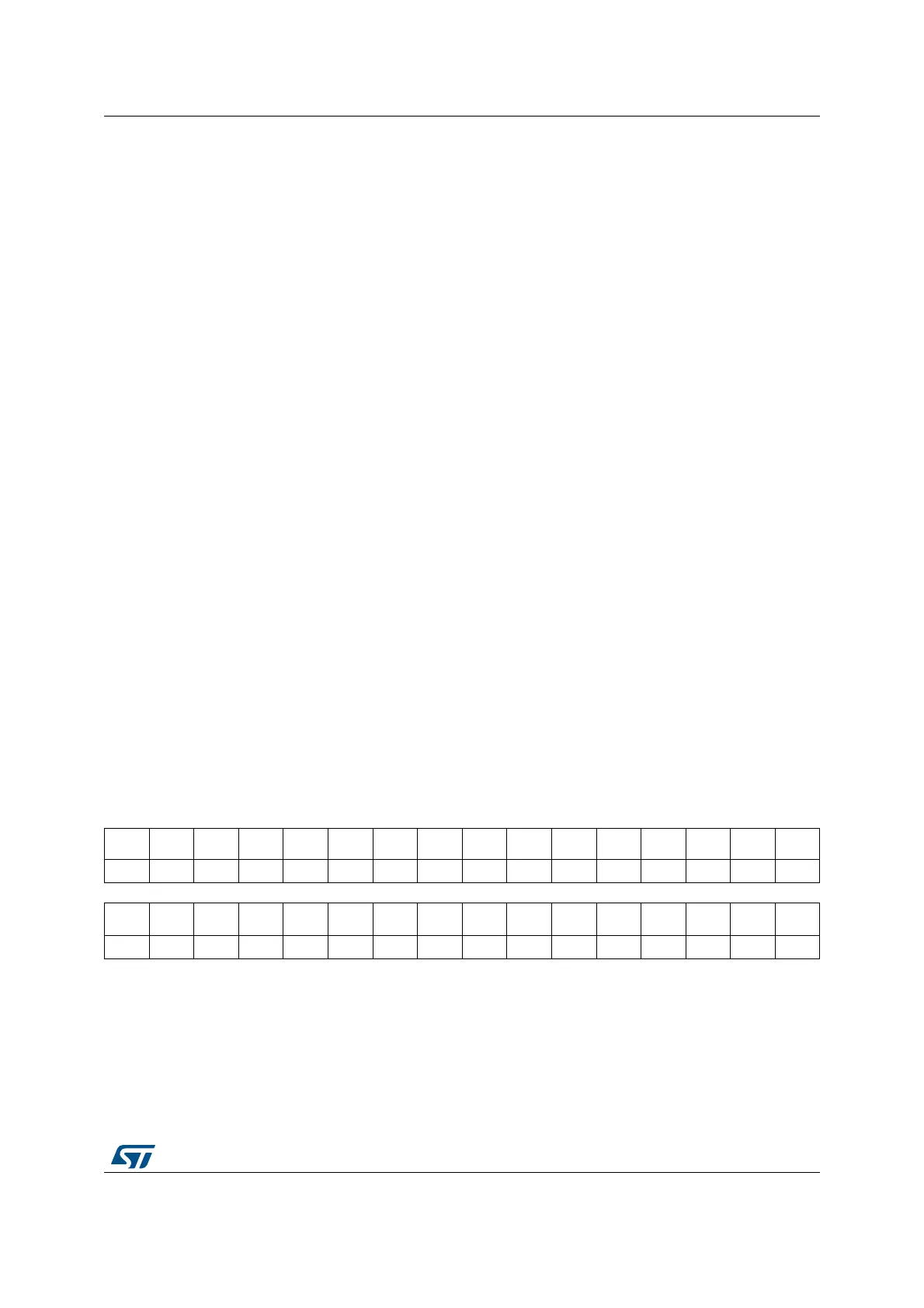

31.15.27 OTG host channel x interrupt register (OTG_HCINTx)

(x = 0..15[HS] / 11[FS], where x = Channel number)

Address offset: 0x508 + (x * 0x20)

Reset value: 0x0000 0000

This register indicates the status of a channel with respect to USB- and AHB-related events.

It is shown in Figure 409. The application must read this register when the host channels

interrupt bit in the core interrupt register (HCINT bit in OTG_GINTSTS) is set. Before the

application can read this register, it must first read the host all channels interrupt

(OTG_HAINT) register to get the exact channel number for the host channel-x interrupt

register. The application must clear the appropriate bit in this register to clear the

corresponding bits in the OTG_HAINT and OTG_GINTSTS registers.

Note: Configuration register for USB OTG FS.

Bit 31 SPLITEN: Split enable

The application sets this bit to indicate that this channel is enabled to perform split

transactions.

Bits 30:17 Reserved, must be kept at reset value.

Bit 16 COMPLSPLT: Do complete split

The application sets this bit to request the OTG host to perform a complete split transaction.

Bits 15:14 XACTPOS[1:0]: Transaction position

This field is used to determine whether to send all, first, middle, or last payloads with each

OUT transaction.

11: All. This is the entire data payload of this transaction (which is less than or equal to 188

bytes)

10: Begin. This is the first data payload of this transaction (which is larger than 188 bytes)

00: Mid. This is the middle payload of this transaction (which is larger than 188 bytes)

01: End. This is the last payload of this transaction (which is larger than 188 bytes)

Bits 13:7 HUBADDR[6:0]: Hub address

This field holds the device address of the transaction translator’s hub.

Bits 6:0 PRTADDR[6:0]: Port address

This field is the port number of the recipient transaction translator.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

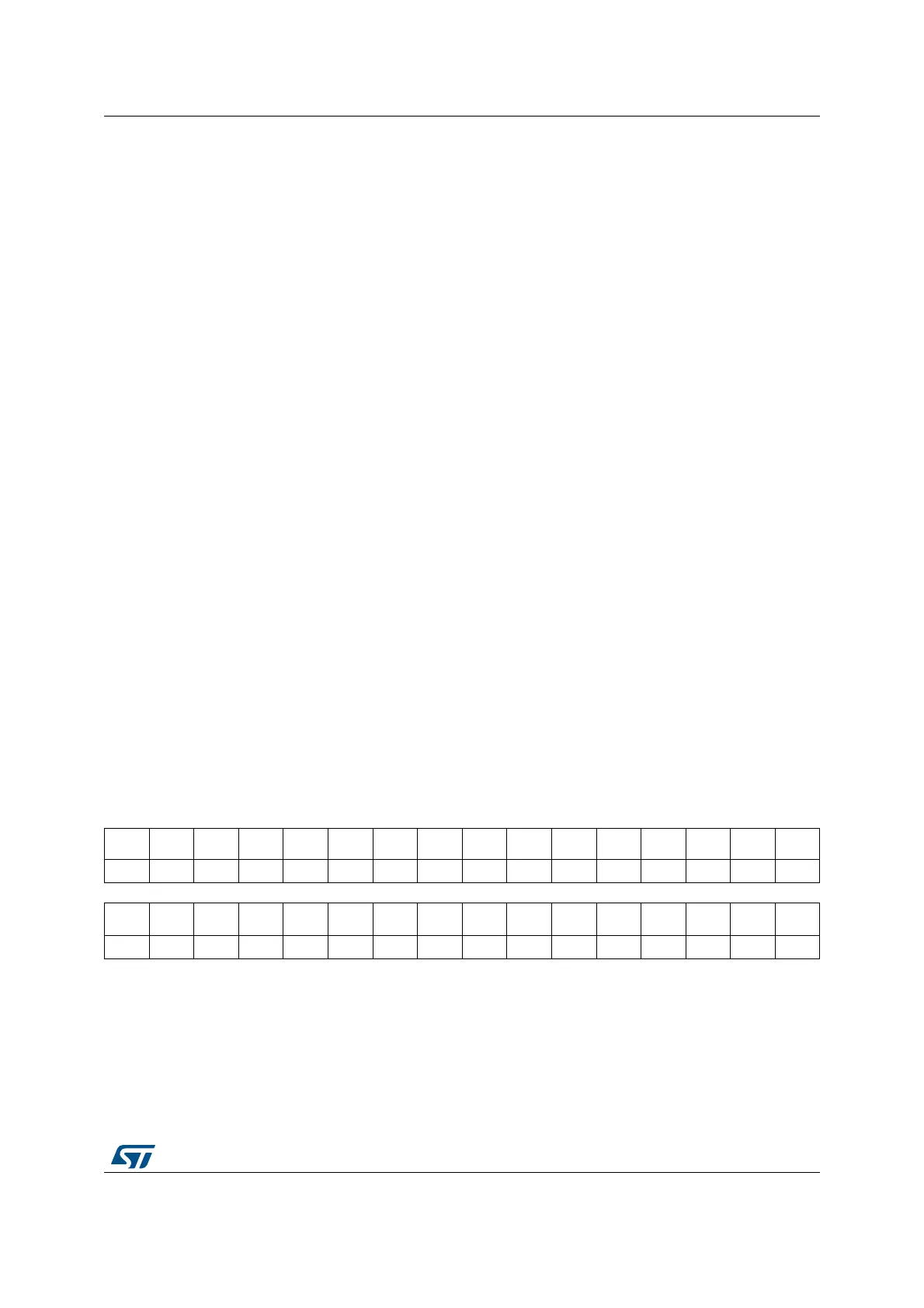

1514131211109876543210

Res. Res. Res. Res. Res. DTERR

FRM

OR

BBERR TXERR Res. ACK NAK STALL Res. CHH XFRC

rc_w1rc_w1rc_w1rc_w1 rc_w1rc_w1rc_w1 rc_w1rc_w1

Loading...

Loading...