Direct memory access controller (DMA) RM0390

208/1328 RM0390 Rev 4

9.3.5 Arbiter

An arbiter manages the 8 DMA stream requests based on their priority for each of the two

AHB master ports (memory and peripheral ports) and launches the peripheral/memory

access sequences.

Priorities are managed in two stages:

• Software: each stream priority can be configured in the DMA_SxCR register. There are

four levels:

– Very high priority

– High priority

– Medium priority

– Low priority

• Hardware: If two requests have the same software priority level, the stream with the

lower number takes priority over the stream with the higher number. For example,

stream 2 takes priority over stream 4.

9.3.6 DMA streams

Each of the 8 DMA controller streams provides a unidirectional transfer link between a

source and a destination.

Each stream can be configured to perform:

• Regular type transactions: memory-to-peripherals, peripherals-to-memory or memory-

to-memory transfers

• Double-buffer type transactions: double buffer transfers using two memory pointers for

the memory (while the DMA is reading/writing from/to a buffer, the application can

write/read to/from the other buffer).

The amount of data to be transferred (up to 65535) is programmable and related to the

source width of the peripheral that requests the DMA transfer connected to the peripheral

AHB port. The register that contains the amount of data items to be transferred is

decremented after each transaction.

9.3.7 Source, destination and transfer modes

Both source and destination transfers can address peripherals and memories in the entire

4 Gbytes area, at addresses comprised between 0x0000 0000 and 0xFFFF FFFF.

The direction is configured using the DIR[1:0] bits in the DMA_SxCR register and offers

three possibilities: memory-to-peripheral, peripheral-to-memory or memory-to-memory

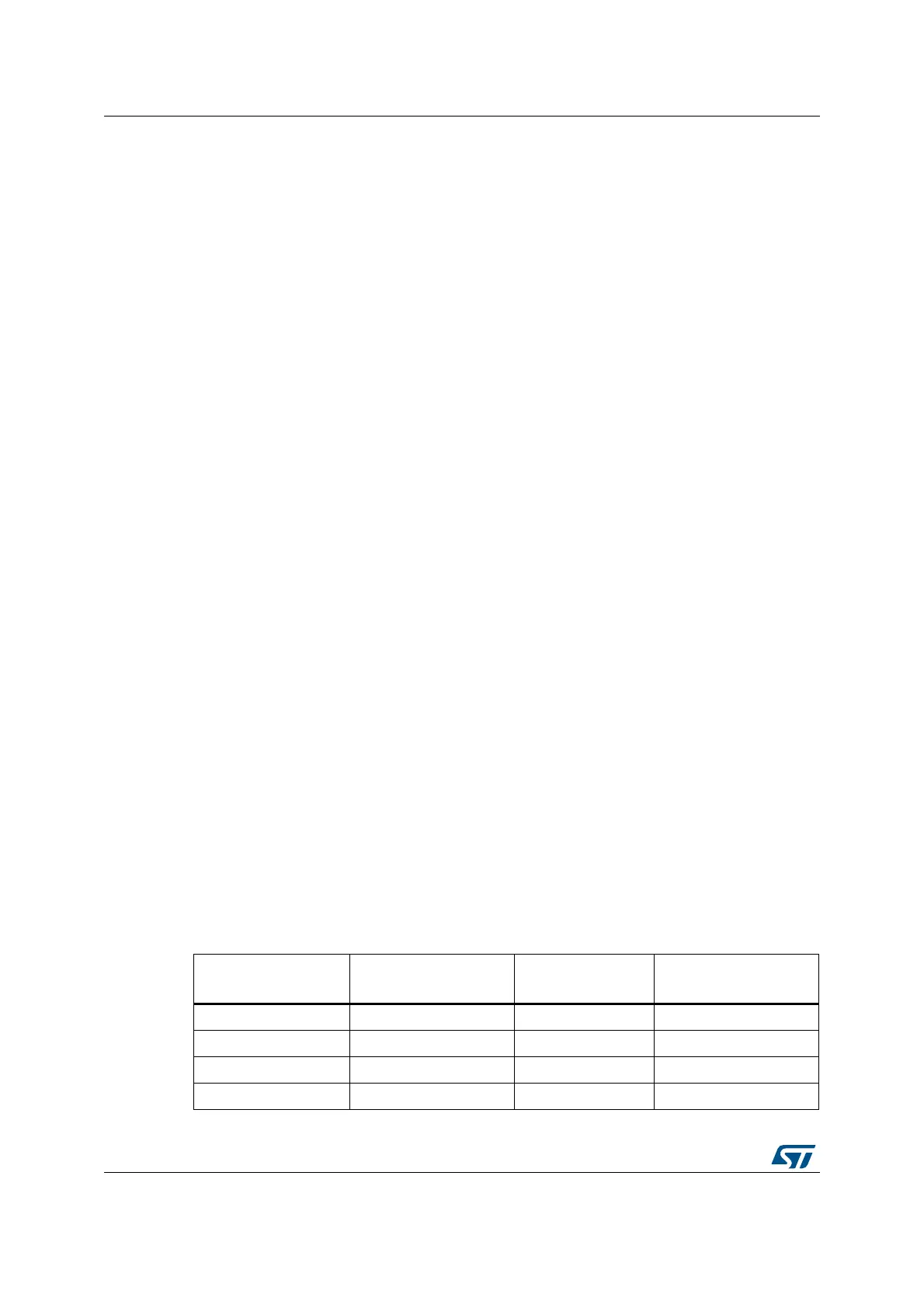

transfers. Table 30 describes the corresponding source and destination addresses.

Table 30. Source and destination address

Bits DIR[1:0] of the

DMA_SxCR register

Direction Source address Destination address

00 Peripheral-to-memory DMA_SxPAR DMA_SxM0AR

01 Memory-to-peripheral DMA_SxM0AR DMA_SxPAR

10 Memory-to-memory DMA_SxPAR DMA_SxM0AR

11 Reserved - -

Loading...

Loading...