Fast-mode Plus Inter-integrated circuit (FMPI2C) interface RM0390

694/1328 RM0390 Rev 4

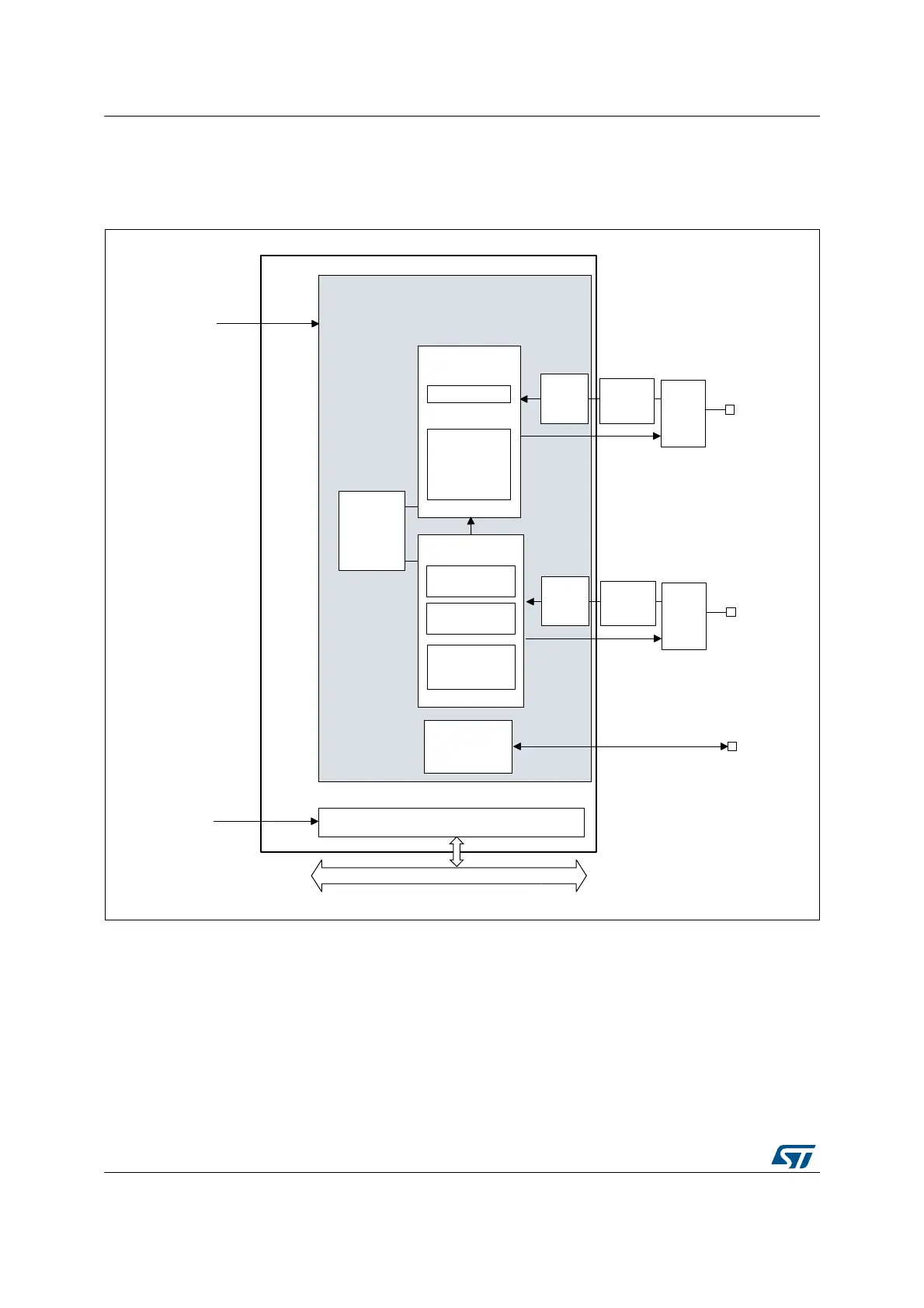

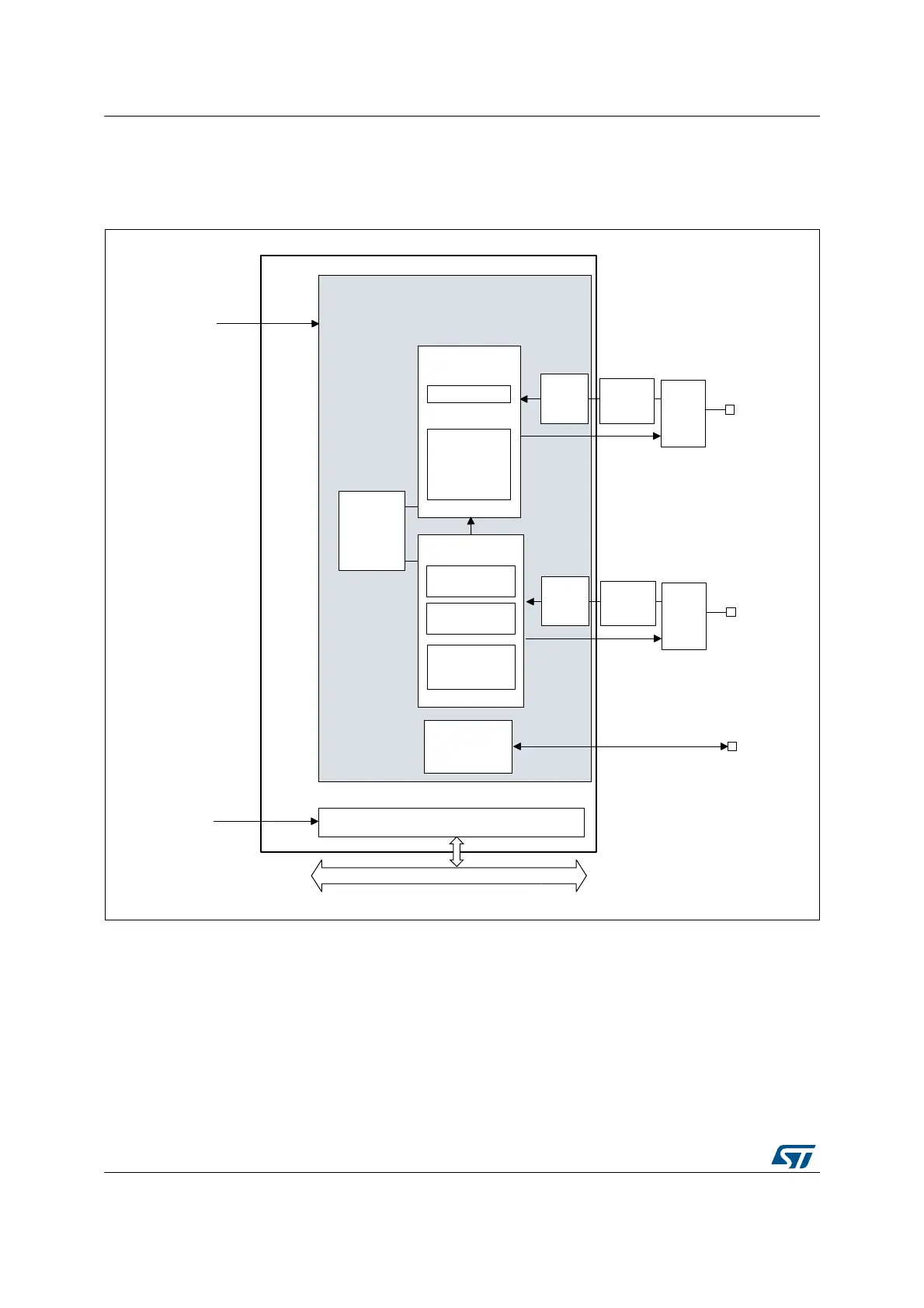

23.4.1 FMPI2C block diagram

The block diagram of the FMPI2C interface is shown in Figure 241.

Figure 241. FMPI2C block diagram

The FMPI2C is clocked by an independent clock source which allows to the FMPI2C to

operate independently from the PCLK frequency.

This independent clock source can be selected from the following three clock sources:

• PCLK1: APB1 clock (default value)

• HSI: high speed internal oscillator

• SYSCLK: system clock

Refer to Section 6: Reset and clock control (RCC) for more details.

06Y9

,&&/.

:DNHXS

RQ

DGGUHVV

PDWFK

60%86

3(&

JHQHUDWLRQ

FKHFN

6KLIWUHJLVWHU

'DWDFRQWURO

60%XV

7LPHRXW

FKHFN

&ORFNFRQWURO

0DVWHUFORFN

JHQHUDWLRQ

6ODYHFORFN

VWUHWFKLQJ

60%XV$OHUW

FRQWURO

VWDWXV

'LJLWDO

QRLVH

ILOWHU

,&B6&/

,&B60%$

5HJLVWHUV

$3%EXV

*3,2

ORJLF

$QDORJ

QRLVH

ILOWHU

'LJLWDO

QRLVH

ILOWHU

,&B6'$

*3,2

ORJLF

$QDORJ

QRLVH

ILOWHU

,FBSFON

,FBNHUBFN

3&/.

Loading...

Loading...