Reset and clock control (RCC) RM0390

144/1328 RM0390 Rev 4

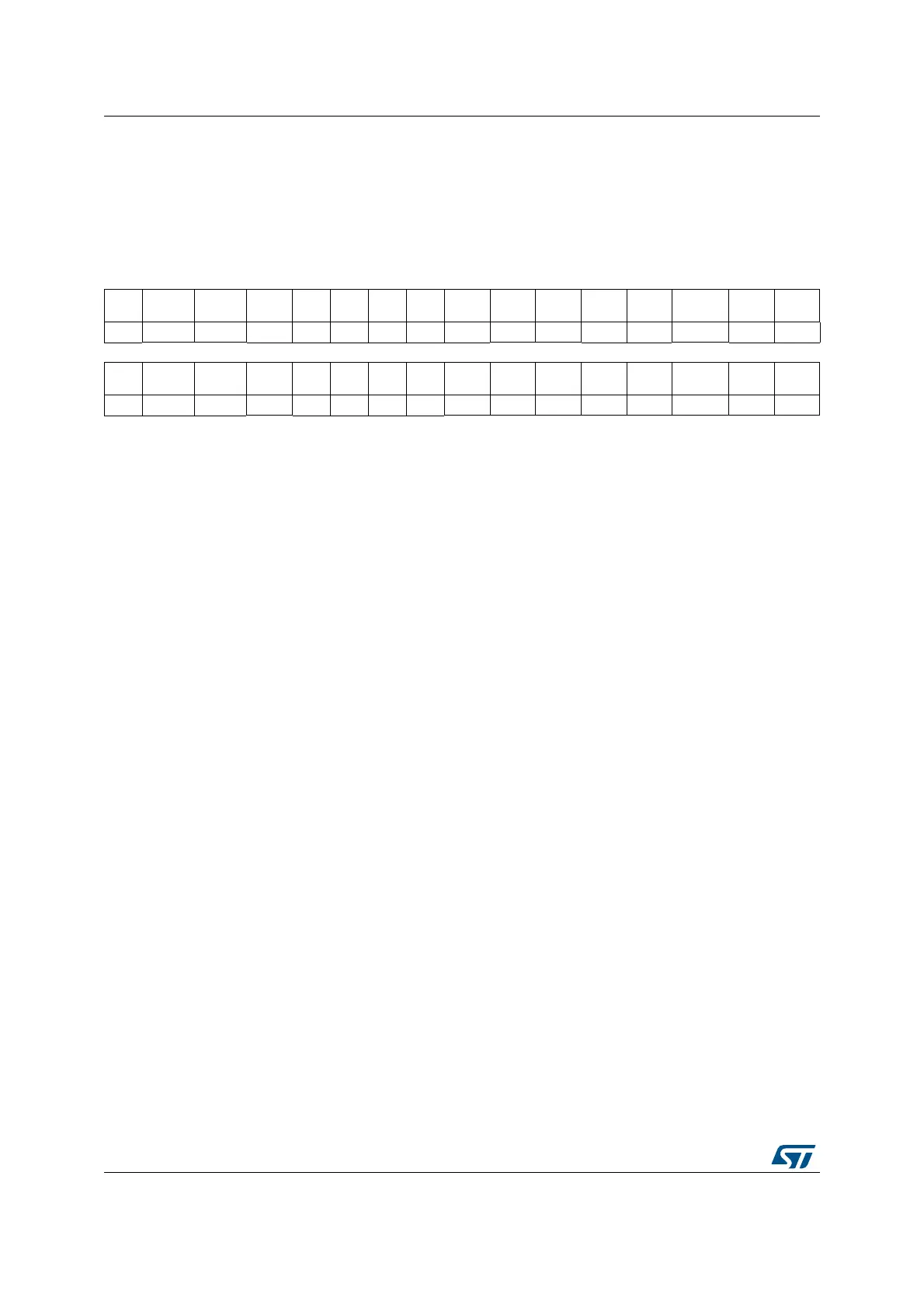

6.3.10 RCC AHB1 peripheral clock enable register (RCC_AHB1ENR)

Address offset: 0x30

Reset value: 0x0010 0000

Access: no wait state, word, half-word and byte access.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res.

OTGHS

ULPIEN

OTGHS

EN

Res. Res. Res. Res. Res. Res.

DMA2

EN

DMA1

EN

Res. Res.

BKP

SRAMEN

Res. Res.

rw rw rw rw rw

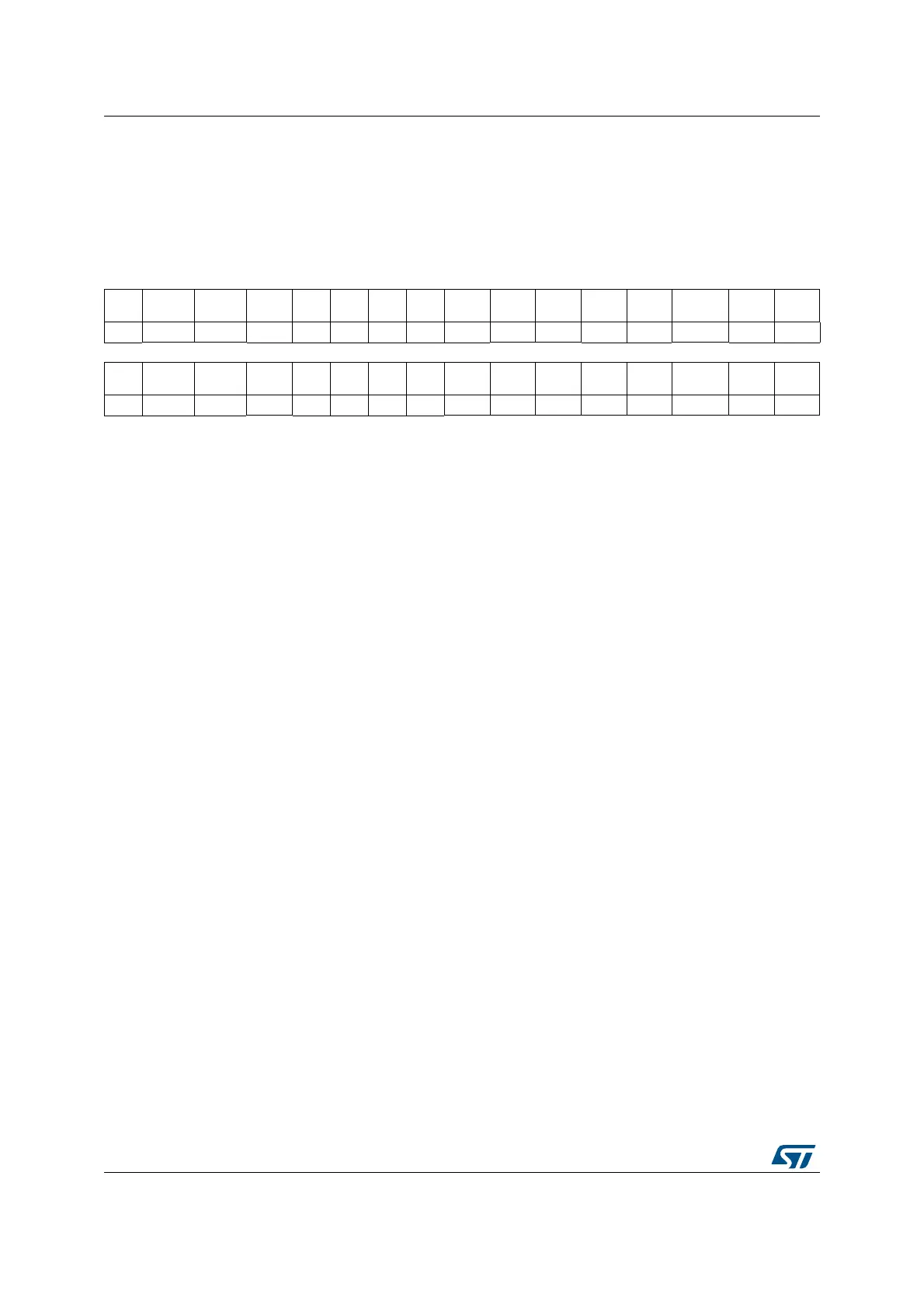

1514131211109876543 2 10

Res. Res. Res.

CRC

EN

Res. Res. Res. Res.

GPIOH

EN

GPIOG

EN

GPIOF

EN

GPIOE

EN

GPIOD

EN

GPIOC

EN

GPIOB

EN

GPIOA

EN

rw rw rw rw rw rw rw rw rw

Bit 31 Reserved, must be kept at reset value.

Bit 30 OTGHSULPIEN: USB OTG HSULPI clock enable

This bit is set and cleared by software.

0: USB OTG HS ULPI clock disabled

1: USB OTG HS ULPI clock enabled

Bit 29 OTGHSEN: USB OTG HS clock enable

This bit is set and cleared by software.

0: USB OTG HS clock disabled

1: USB OTG HS clock enabled

Bits 28:23 Reserved, must be kept at reset value.

Bit 22 DMA2EN: DMA2 clock enable

This bit is set and cleared by software.

0: DMA2 clock disabled

1: DMA2 clock enabled

Bit 21 DMA1EN: DMA1 clock enable

This bit is set and cleared by software.

0: DMA1 clock disabled

1: DMA1 clock enabled

Bits 20:19 Reserved, must be kept at reset value.

Bit 18 BKPSRAMEN: Backup SRAM interface clock enable

This bit is set and cleared by software.

0: Backup SRAM interface clock disabled

1: Backup SRAM interface clock enabled

Bits 17:13 Reserved, must be kept at reset value.

Bit 12 CRCEN: CRC clock enable

This bit is set and cleared by software.

0: CRC clock disabled

1: CRC clock enabled

Bits 11:8 Reserved, must be kept at reset value.

Loading...

Loading...