USB on-the-go full-speed/high-speed (OTG_FS/OTG_HS) RM0390

1180/1328 RM0390 Rev 4

31.15.51 OTG device IN endpoint x DMA address register (OTG_DIEPDMAx)

(x = 0..8, where x = endpoint number)

Address offset: 0x914 + (x * 0x20)

Reset value: 0x0000 0000

Note: Configuration register applies only to USB OTG HS

31.15.52 OTG device IN endpoint transmit FIFO status register

(OTG_DTXFSTSx) (x = 0..5[FS] /8[HS], where

x = endpoint number)

Address offset for IN endpoints: 0x918 + (x * 0x20) This read-only register contains the free

space information for the device IN endpoint Tx FIFO.

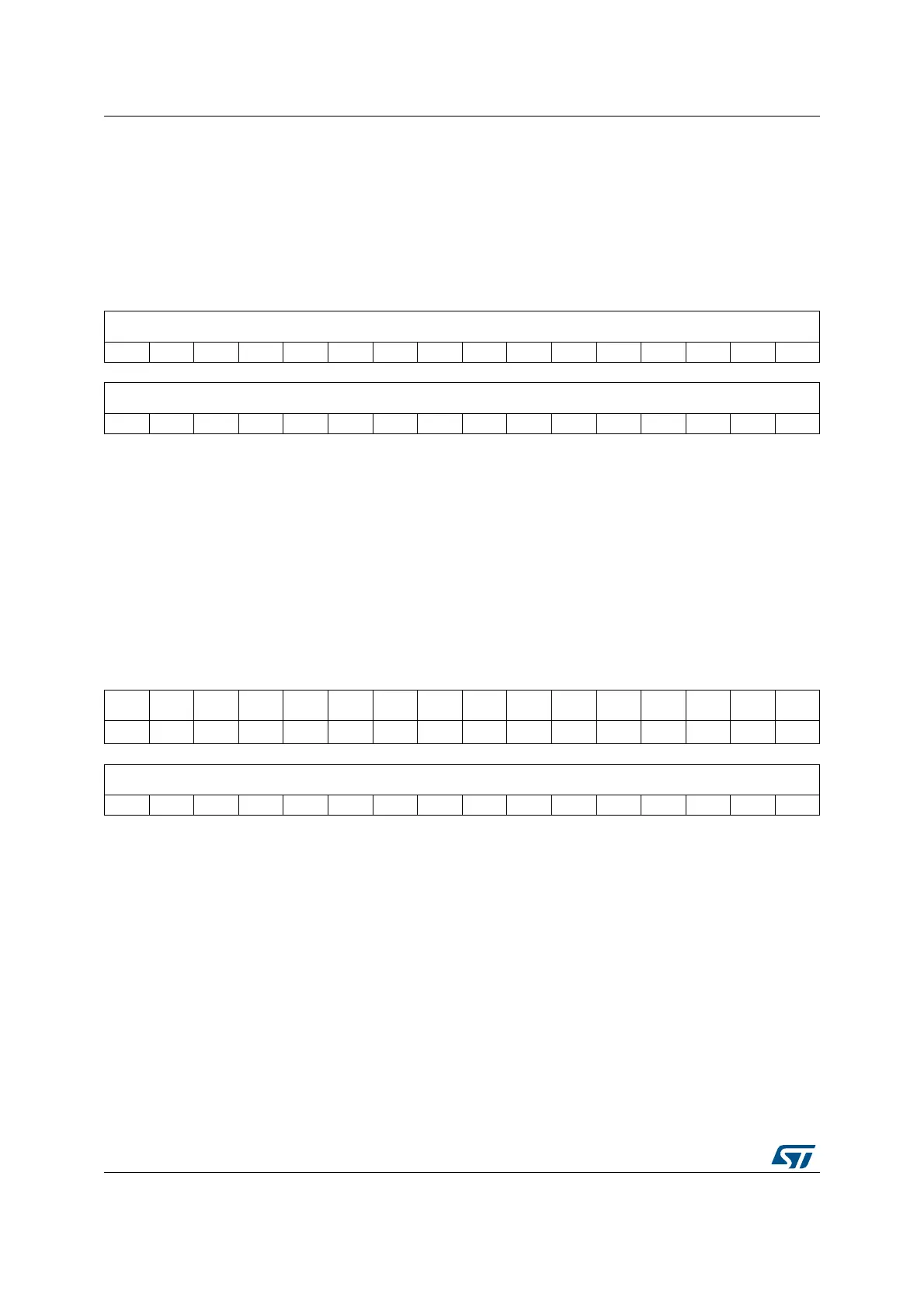

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

DMAADDR[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

DMAADDR[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 DMAADDR[31:0]: DMA Address

This field holds the start address in the external memory from which the data for the

endpoint must be fetched. This register is incremented on every AHB transaction.

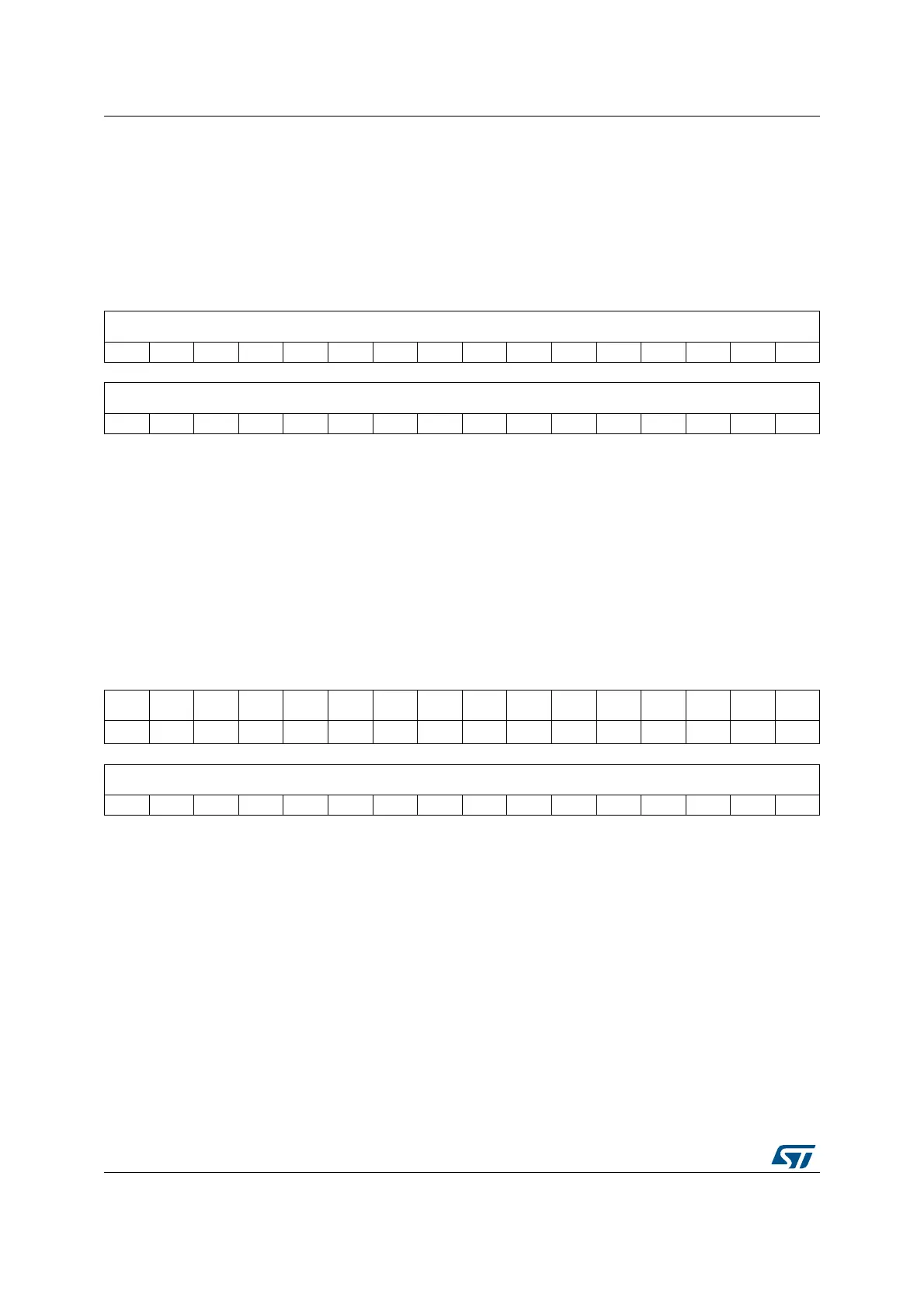

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

INEPTFSAV[15:0]

rrrrrrrrrrrrrrrr

31:16 Reserved, must be kept at reset value.

15:0 INEPTFSAV[15:0]: IN endpoint Tx FIFO space available

Indicates the amount of free space available in the endpoint Tx FIFO.

Values are in terms of 32-bit words:

0x0: Endpoint Tx FIFO is full

0x1: 1 word available

0x2: 2 words available

0xn: n words available

Others: Reserved

Loading...

Loading...