RM0390 Rev 4 197/1328

RM0390 System configuration controller (SYSCFG)

202

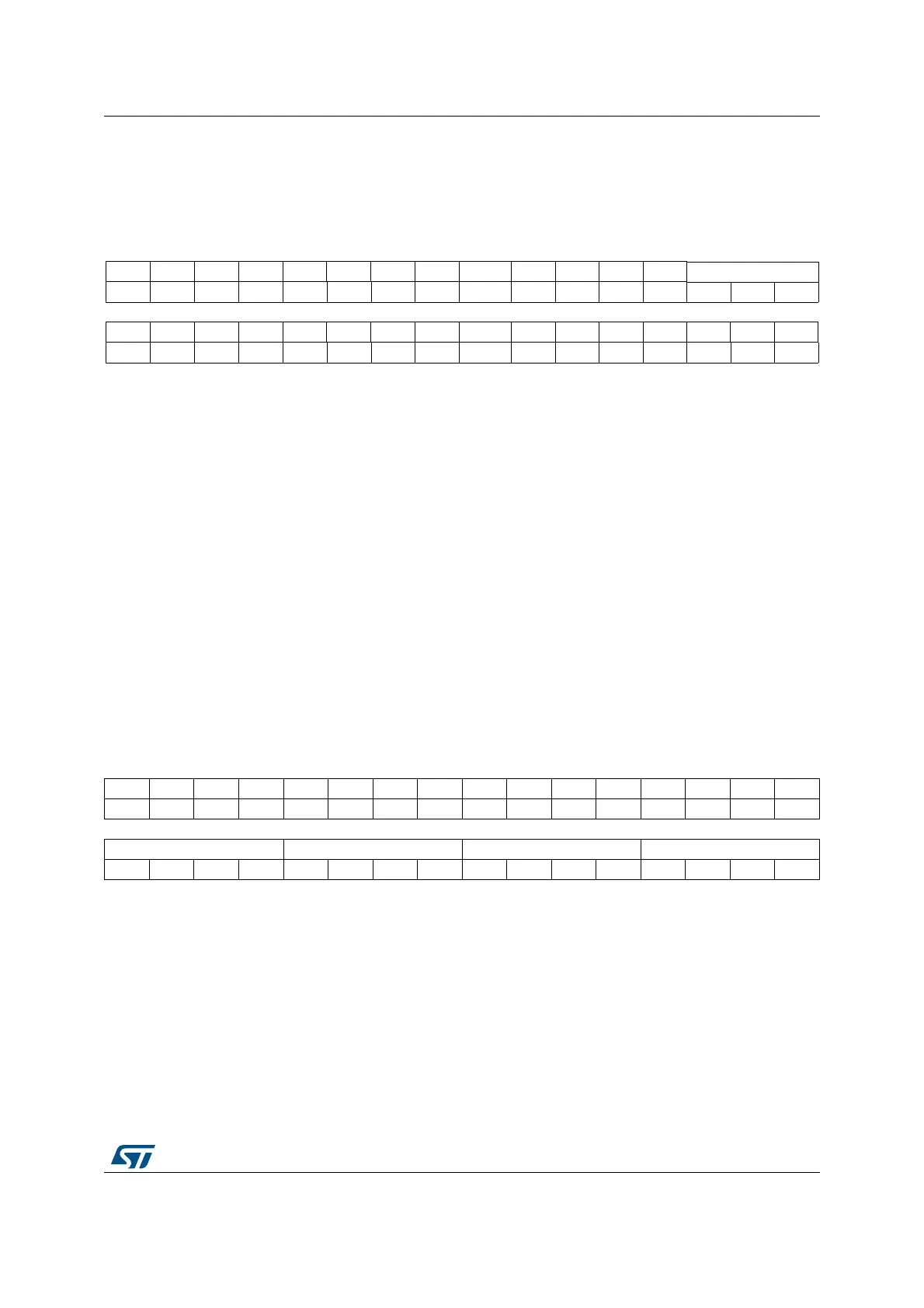

8.2.2 SYSCFG peripheral mode configuration register (SYSCFG_PMC)

Address offset: 0x04

Reset value: 0x0000 0000

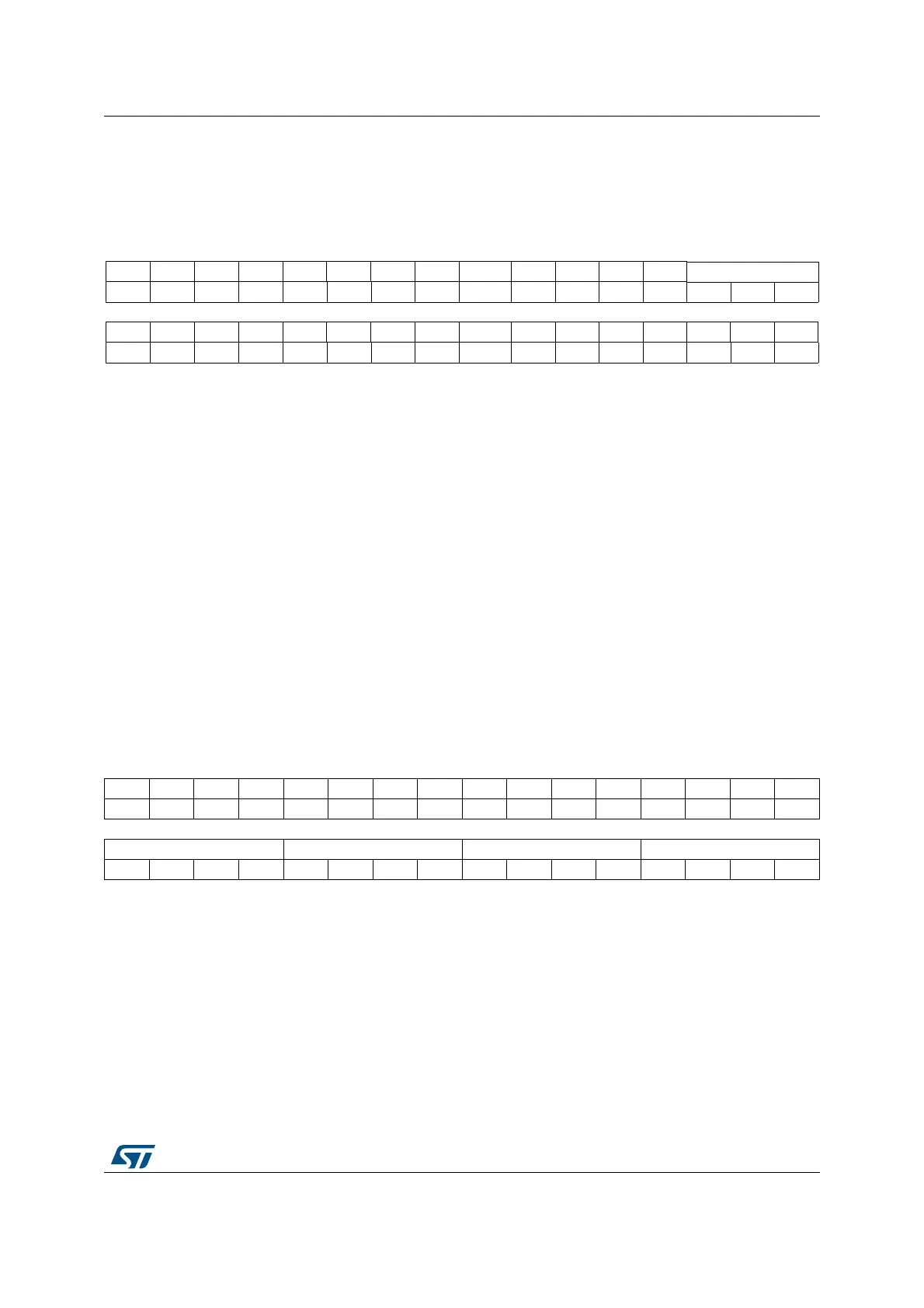

8.2.3 SYSCFG external interrupt configuration register 1

(SYSCFG_EXTICR1)

Address offset: 0x08

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. ADCxDC2

rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

Bits 31:19 Reserved, must be kept at reset value.

Bits 18:16 ADCxDC2:

0: No effect.

1: Refer to AN4073 on how to use this bit.

Note: These bits can be set only if the following conditions are met:

- ADC clock higher or equal to 30 MHz.

- Only one ADCxDC2 bit must be selected if ADC conversions do not start

at the same time and the sampling times differ.

- These bits must not be set when the ADCDC1 bit is set in PWR_CR

register.

Bits 15:0 Reserved, must be kept at reset value.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

EXTI3[3:0] EXTI2[3:0] EXTI1[3:0] EXTI0[3:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...