RM0390 Rev 4 909/1328

RM0390 SPDIF receiver interface (SPDIFRX)

929

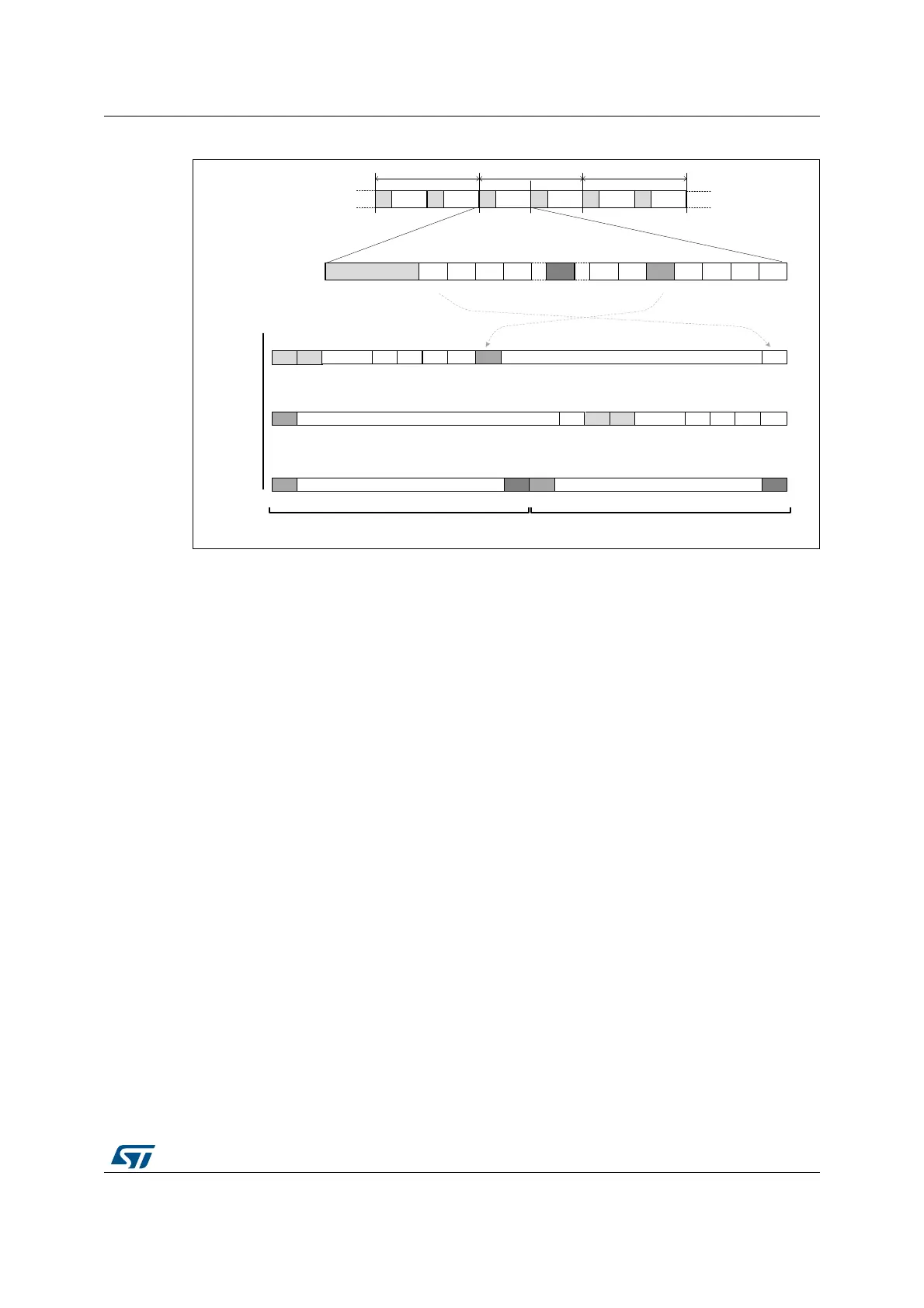

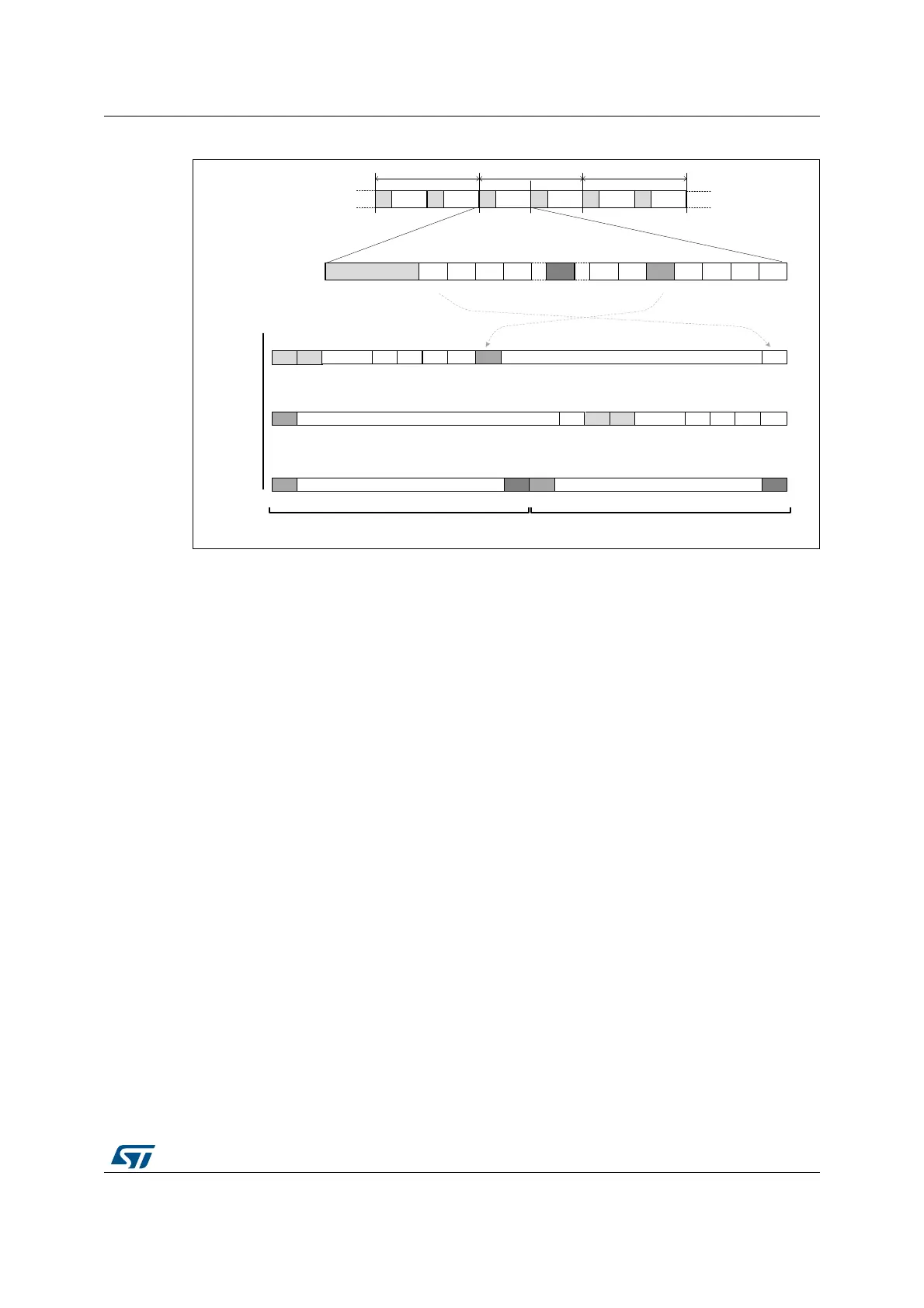

Figure 349. SPDIFRX_DR register format

Setting DRFMT to 0b00 or 0b01, offers the possibility to have the data either right or left

aligned into the SPDIFRX_DR register. The status information can be enabled or forced to

zero according to the way the software wants to handle them.

The format given by DRFMT= 0b10 is interesting in non-linear mode, as only 16 bits per

sub-frame are used. By using this format, the data of two consecutive sub-frames are stored

into SPDIFRX_DR, dividing by two the amount of memory footprint. Note that when

RXSTEO = 1, there is no misalignment risks (i.e. data from ChA will be always stored into

SPDIFRX_DR[31:16]). If RXSTEO = 0, then there is a misalignment risk is case of overrun

situation. In that case SPDIFRX_DR[31:16] will always contain the oldest value and

SPDIFRX_DR[15:0] the more recent value (see Figure 351).

In this format the status information cannot be mixed with data, but the user can still get

them through SPDIFRX_CSR register, and use a dedicated DMA channel or interrupt to

transfer them to memory (see Section 27.3.7: Dedicated control flow)

Mixing data and control flow

The user can choose to use this mode in order to get the full flexibility of the handling of the

control flow. The user can select which field shall be kept into the data register

(SPDIFRX_DR).

• When bit PMSK = 1, the Parity Error information is masked (set to 0), otherwise it is

copied into SPDIFRX_DR.

• When bit VMSK = 1, the Validity information is masked (set to 0), otherwise it is copied

into SPDIFRX_DR.

• When bit CUMSK = 1, the Channel Status, and Used data information are masked (set

to 0), otherwise they are copied into SPDIFRX_DR.

• When bit PTMSK = 1, the Preamble Type is masked (set to 0), otherwise it is copied

into SPDIFRX_DR.

37>@RU &RU 8RU 3(RU

'5)07 E

'5>@

06E /6E

37>@RU &RU 8RU 3(RU

'5>@

06E /6E

'5)07 E

9RU

9RU

06E /6E

'5)07 E

06E /6E

'51/>@ '51/>@

66\QF3UHDPEOH 6 6 6 66 6 3&9 8

,(&VXEIUDPH

/6E 06E

6

6

6 66 6

6

0 &K$ : &K% % &K$ : &K% 0 &K$ : &K%

)UDPH )UDPH)UDPH

&K$ &K%

,(&EORFNIRUPDW

6

6

63',)5;B'5

06Y9

Loading...

Loading...