SPDIF receiver interface (SPDIFRX) RM0390

912/1328 RM0390 Rev 4

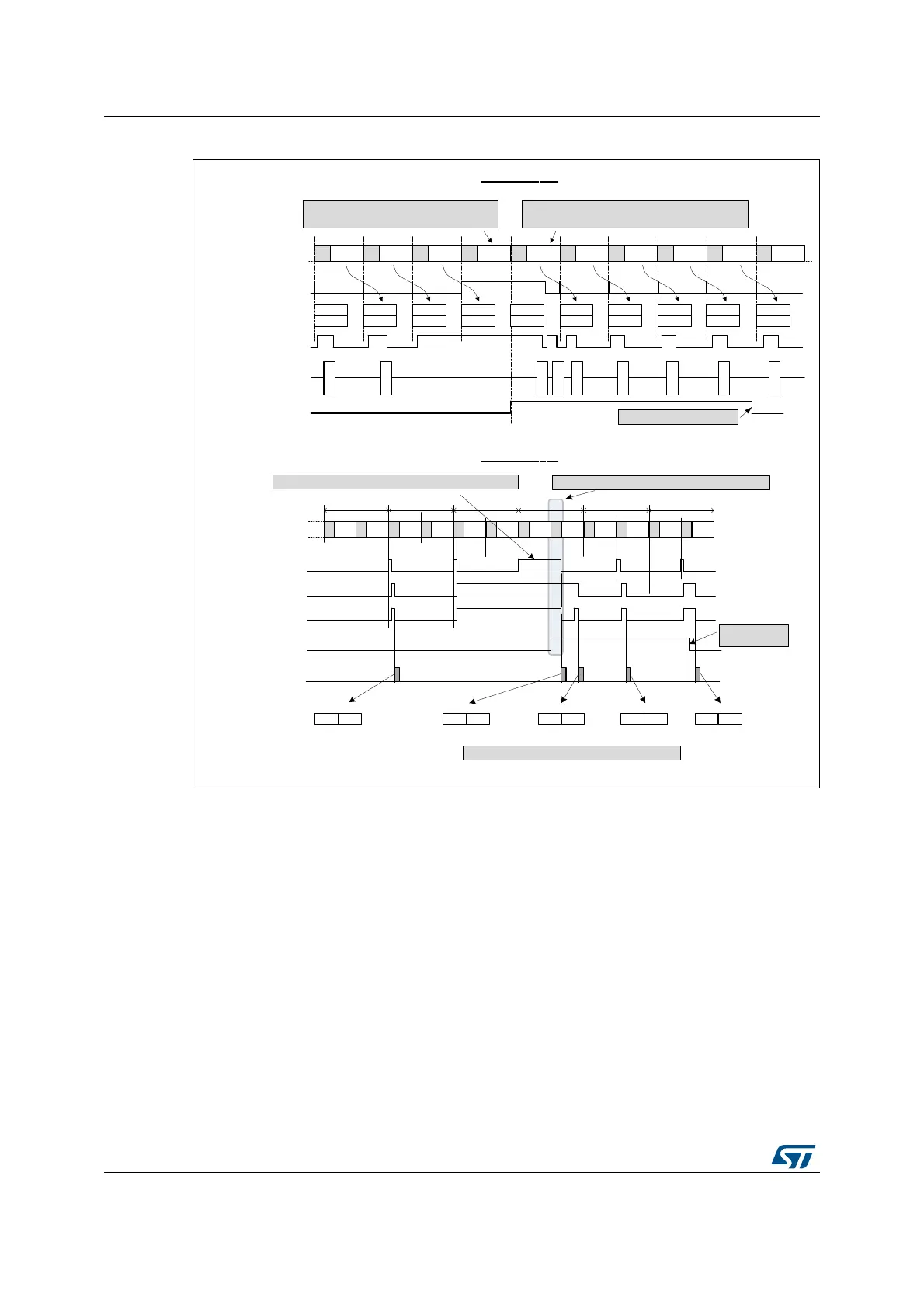

Figure 351. S/PDIF overrun error when RXSTEO = 0

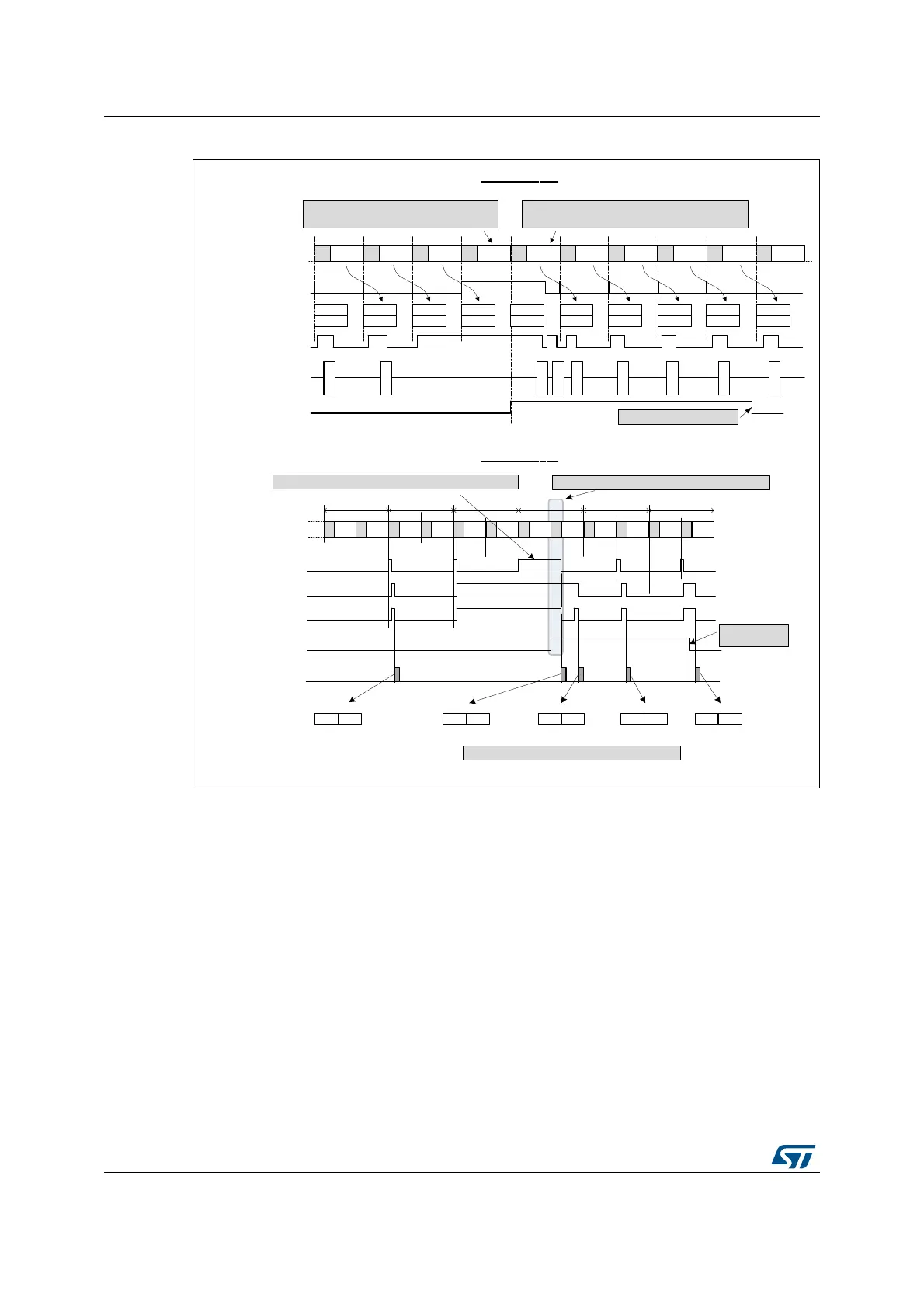

If the RXSTEO bit is set to 1, it means that stereo data are transported, then the SPDIFRX

has to avoid misalignment between left and right channels. So the peripheral has to drop a

second sample even if there is room inside the RX_BUF in order to avoid misalignment.

Then the incoming samples can be written normally into the RX_BUF even if the OVR flag is

still pending. Refer to Figure 352.

The OVR flag is cleared by software, by setting the OVRCF bit to 1.

0 &K$ : &K% % &K$ : &K% 0 &K$ : &K% 0 &K$ : &K% % &K$ : &K%

5;B%8))8//

&K%

63',)5;B'0$B5(4

5;B%8)DQG

63',)5;B'5FRQWHQW

&K$

&K%

&K%

&K$

&K$

&K%

&K$

&K%

&K$

&K%

&K$

63',)5;B,1

63',)5;B,54295

$FNQRZOHGJHGE\6:

&K%FDQQRWEHZULWWHQLQWRWKH5;B%8)

EHFDXVHLWLV)8//Î2YHUUXQ

&K$FDQEHZULWWHQLQWRWKH5;B%8)

&K%

&K$

&K%

&K$

&K%

&K$

&K%

&K$

6DPSOHVVWRUHGLQWR

PHPRU\

&K$

0 ' : ' % ' : ' 0 ' : '

)UDPH )UDPH)UDPH

,(&EORFNIRUPDW

&K$ &K% &K$ &K% &K$ &K%

0 ' : '

)UDPH

&K$ &K%

0 ' : '

)UDPH

&K$ &K%

0 ' : '

)UDPH

&K$ &K%

' '

63',)5;B'5

'DWDUHDGIURP

63',)5;B'5

5;B%8)FDQQRWEHHPSWLHGEHFDXVH63',)B5;LV)8//

63',)5;B'0$B5(4

' '

63',)5;B'5

5;B%8))8//

'LVORVW63',)5;>@FRQWDLQVWKHROGHVWGDWD

63',)5;B,54295

$FNQRZOHGJHG

E\6:

'5)07 E[

'5)07 E

5;1(

'LVDYDLODEOHDQG5;B%8)LV)8//Î2YHUUXQ

' '

63',)5;B'5

' '

63',)5;B'5

' '

63',)5;B'5

06Y9

Loading...

Loading...