RM0390 Rev 4 227/1328

RM0390 Direct memory access controller (DMA)

237

9.5.5 DMA stream x configuration register (DMA_SxCR) (x = 0..7)

This register is used to configure the concerned stream.

Address offset: 0x10 + 0x18 * stream number

Reset value: 0x0000 0000

Bits 24, 18, 8, 2 CDMEIFx: stream x clear direct mode error interrupt flag (x = 7..4)

Writing 1 to this bit clears the corresponding DMEIFx flag in the DMA_HISR register.

Bits 23, 17, 7, 1 Reserved, must be kept at reset value.

Bits 22, 16, 6, 0 CFEIFx: stream x clear FIFO error interrupt flag (x = 7..4)

Writing 1 to this bit clears the corresponding CFEIFx flag in the DMA_HISR register.

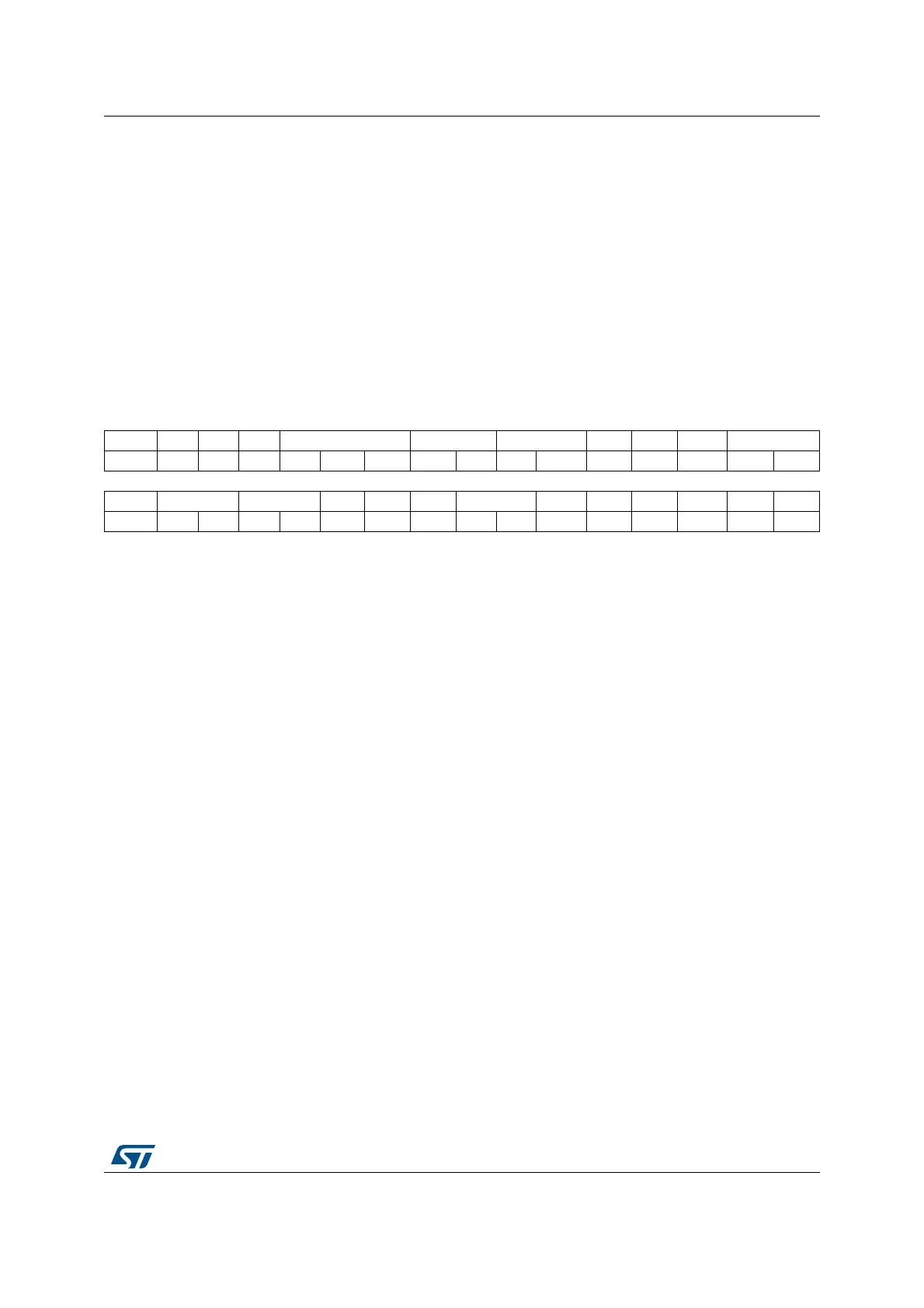

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. CHSEL[2:0] MBURST [1:0] PBURST[1:0] Res. CT DBM PL[1:0]

rw rw rw rw rw rw rw rw rw rw rw

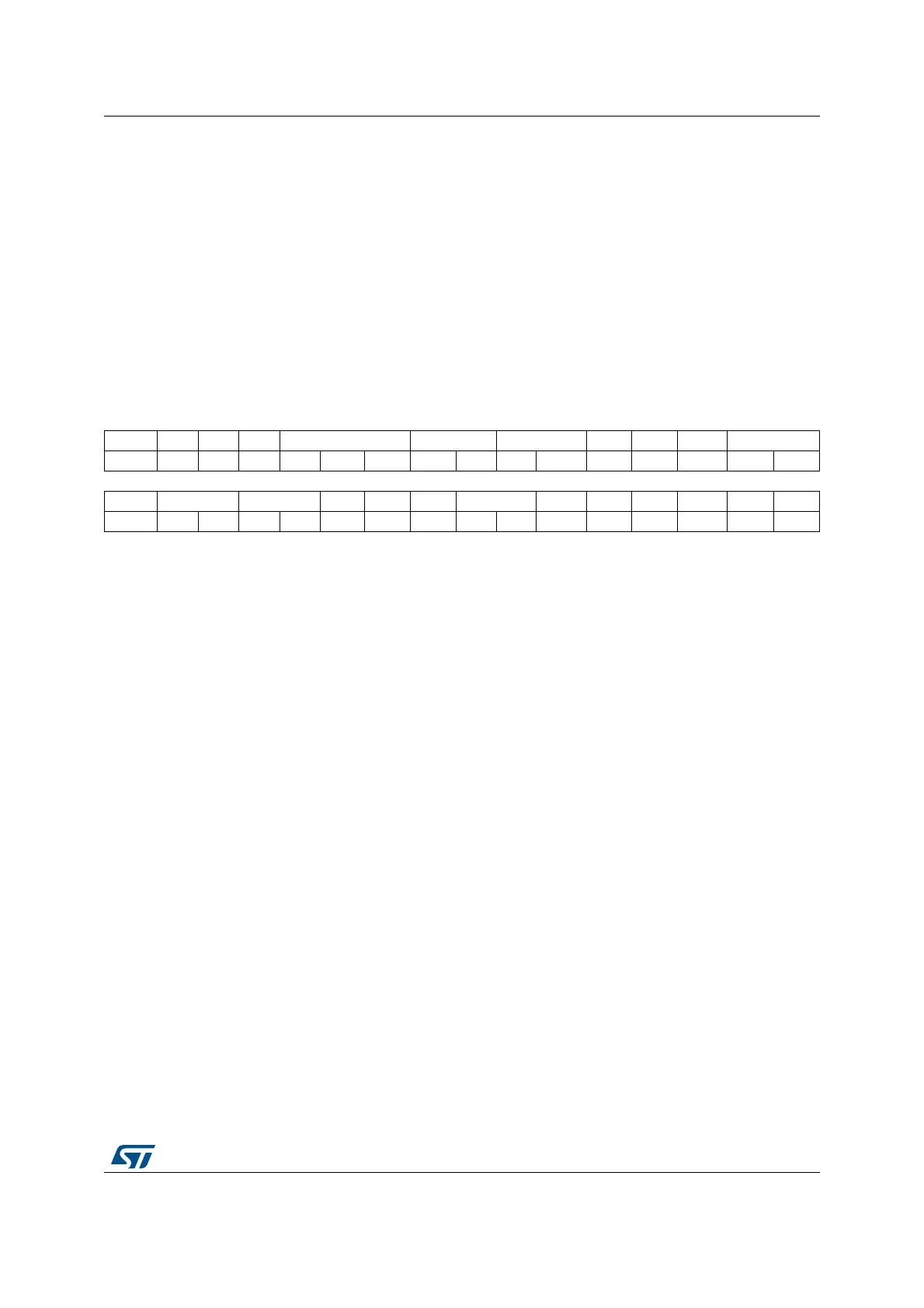

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

PINCOS MSIZE[1:0] PSIZE[1:0] MINC PINC CIRC DIR[1:0] PFCTRL TCIE HTIE TEIE DMEIE EN

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:28 Reserved, must be kept at reset value.

Bits 27:25 CHSEL[2:0]: channel selection

These bits are set and cleared by software.

000: channel 0 selected

001: channel 1 selected

010: channel 2 selected

011: channel 3 selected

100: channel 4 selected

101: channel 5 selected

110: channel 6 selected

111: channel 7 selected

These bits are protected and can be written only if EN is ‘0’.

Bits 24:23 MBURST[1:0]: memory burst transfer configuration

These bits are set and cleared by software.

00: single transfer

01: INCR4 (incremental burst of 4 beats)

10: INCR8 (incremental burst of 8 beats)

11: INCR16 (incremental burst of 16 beats)

These bits are protected and can be written only if EN is ‘0’.

In direct mode, these bits are forced to 0x0 by hardware as soon as bit EN= '1'.

Bits 22:21 PBURST[1:0]: peripheral burst transfer configuration

These bits are set and cleared by software.

00: single transfer

01: INCR4 (incremental burst of 4 beats)

10: INCR8 (incremental burst of 8 beats)

11: INCR16 (incremental burst of 16 beats)

These bits are protected and can be written only if EN is ‘0’.

In direct mode, these bits are forced to 0x0 by hardware.

Bit 20 Reserved, must be kept at reset value.

Loading...

Loading...