RM0390 Rev 4 905/1328

RM0390 SPDIF receiver interface (SPDIFRX)

929

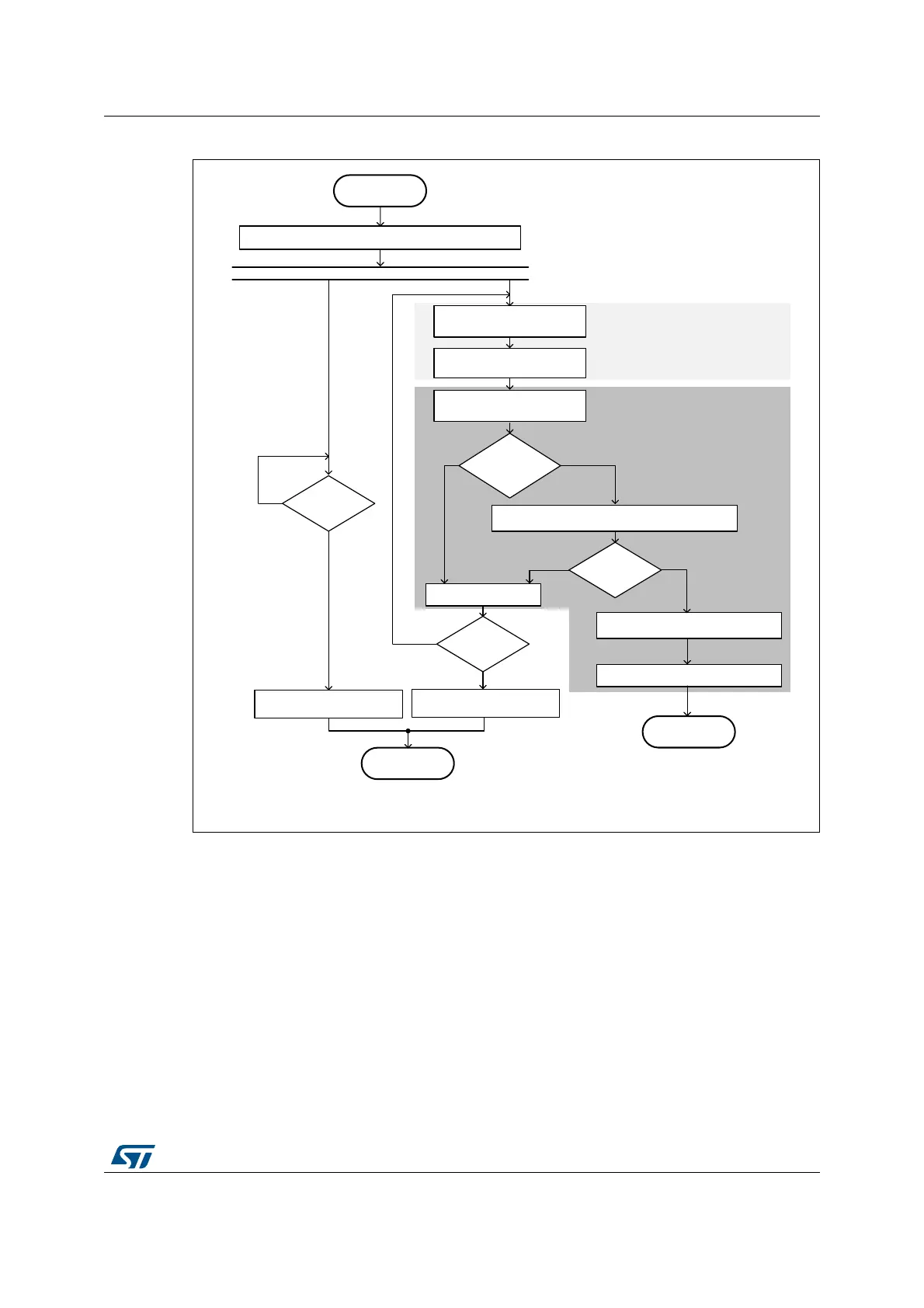

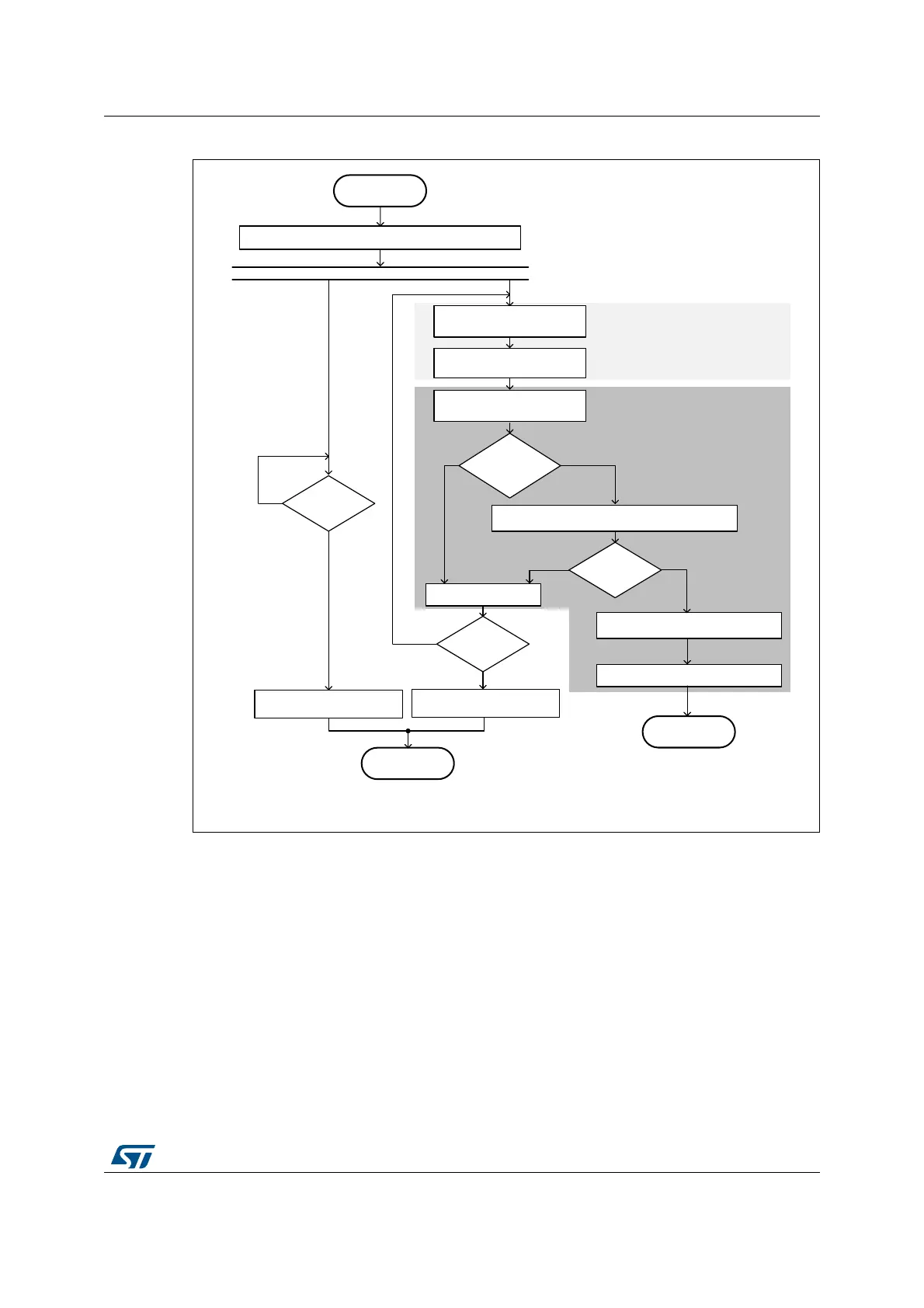

Figure 346. Synchronization flowchart

Refer to Frame structure and synchronization error for additional information concerning

TRCNT overflow.

The FINE SYNC process is re-triggered every frame in order to update thresholds as shown

in Figure 347 in order to continuously track S/PDIF synchronization.

,QLWLDO6\QF

3URFHVV

6HDUFKIRU/RQJHVW6KRUWHVW

SXOVHVIRUWUDQVLWLRQV

&RPSXWH&2$56(WKUHVKROGV

7+

/2

7+

+,

6HDUFKIRUSUHDPEOHIRU

WUDQVLWLRQV

SUHDPEOH

IRXQGZLWKLQ

WUDQV"

6\PE

GHFRGLQJ

2."

&RPSXWH),1(WKUHVKROGV7+

/2

7+

+,

6HW6<1&'WR

$77(037

$77(037

1%75"

6\QFKURQL]DWLRQ

GRQH

(55256\QFIDLOXUH

6(55

6\QFVWRSSHG

<

<

<

1

1

1

&2$56(6<1&

),1(6<1&

3DUDOOHOIORZV

75&17

RYHUIORZV"

<

1

(55256\QFIDLOXUH

7(55

:DLWIRUWUDQVLWLRQVLI:)$ HOVHVNLSWKLVVWHS

06Y9

ā7KHGHFRGLQJLVFRQVLGHUHG2.ZKHQWKHV\PEROVDUHSURSHUO\GHFRGHGDQGSUHDPEOHRFFXUVDWWKHH[SHFWHGSRVLWLRQ

'HFRGHSURSHUO\WKHQH[WV\PEROV

0HDVXUHPHQWRIDQGV\PEROVGXUDWLRQ:,'7+:,'7+

Loading...

Loading...