Universal synchronous asynchronous receiver transmitter (USART) RM0390

798/1328 RM0390 Rev 4

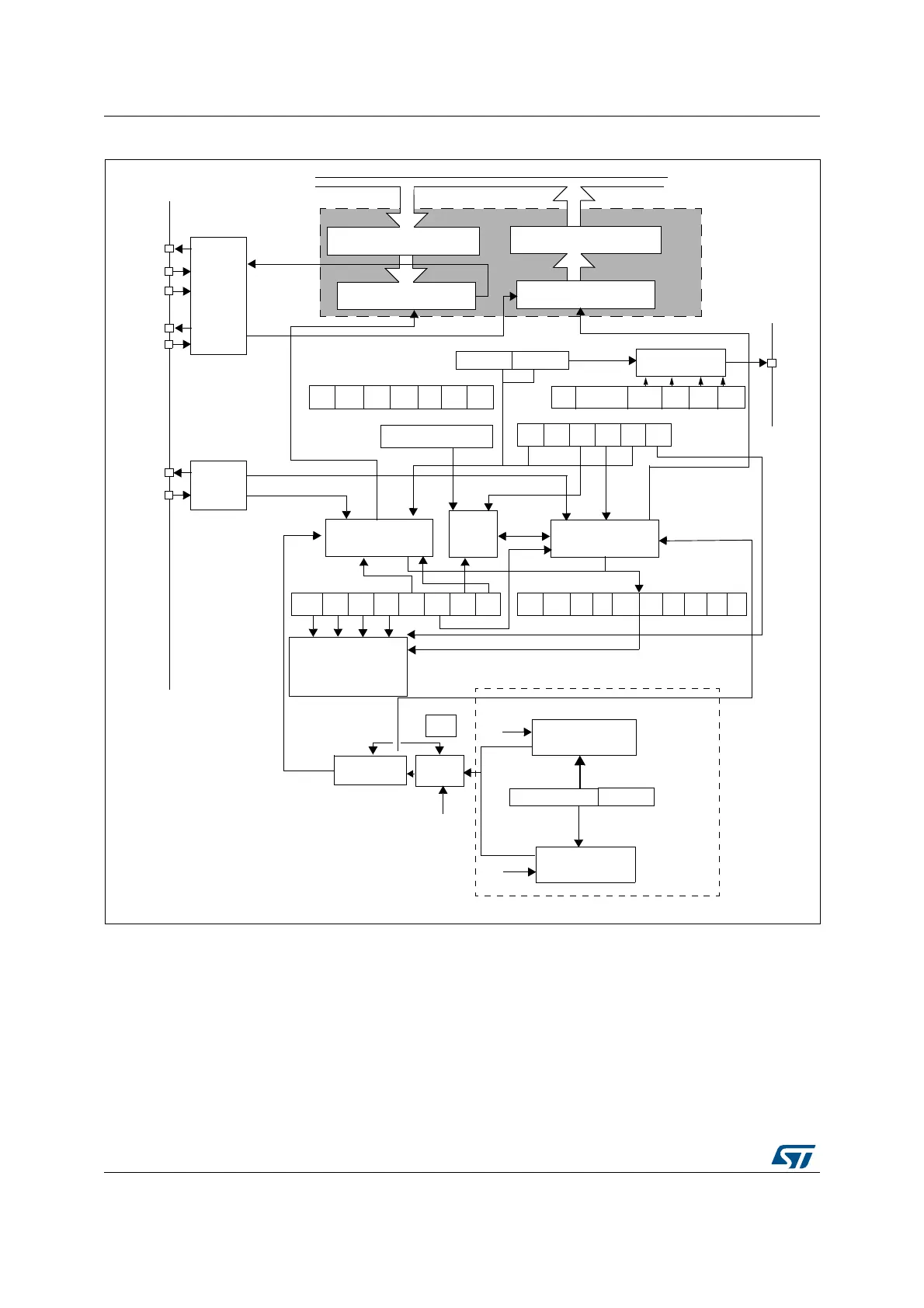

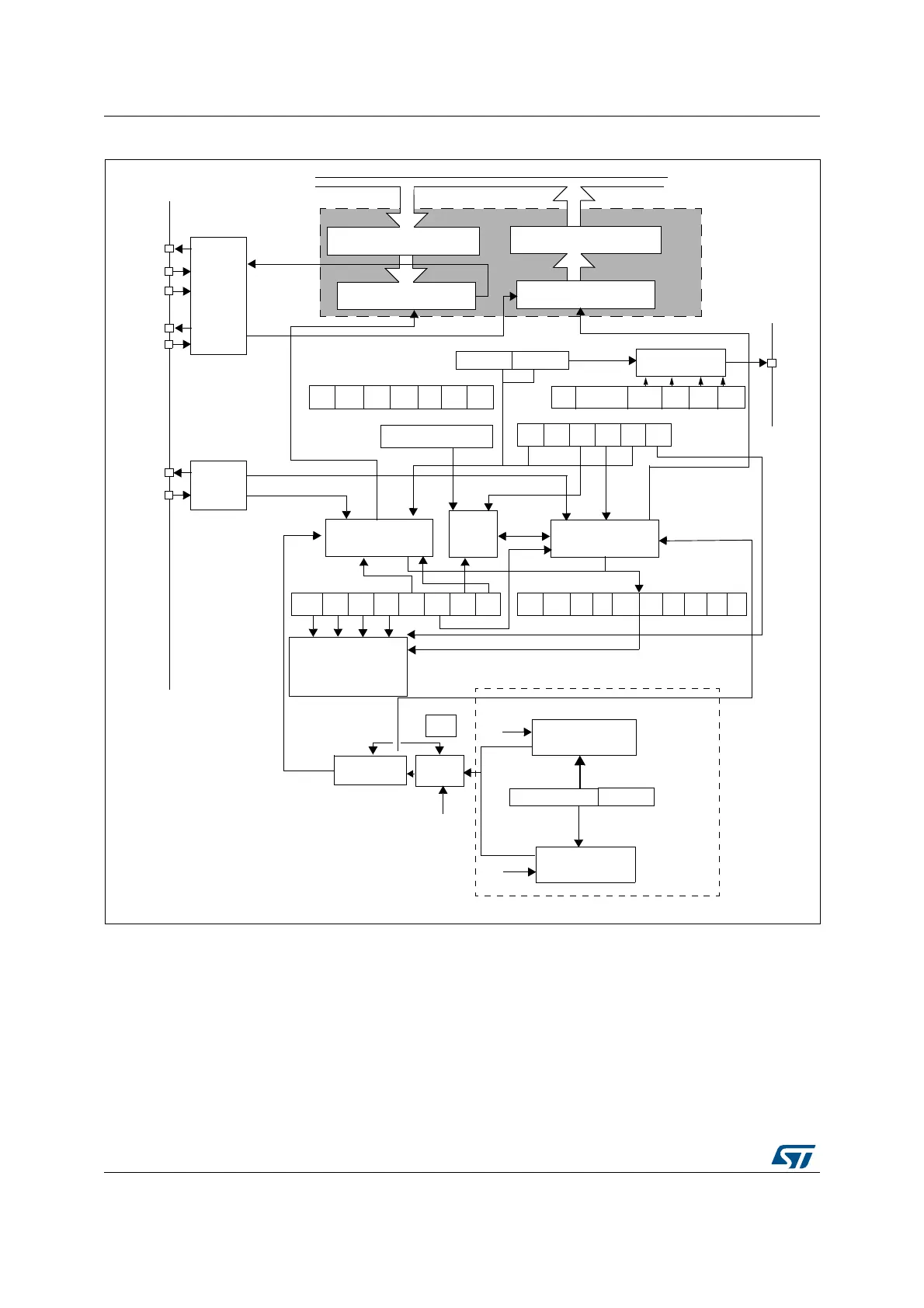

Figure 279. USART block diagram

Wakeup

unit

Receiver

control

SR

Transmit

control

TXETC RXNEIDLEORE NF FE

USART

control

interrupt

CR1

M WAKE

Receive data register (RDR)

Receive Shift Register

Read

Transmit data register (TDR)

Transmit Shift Register

Write

SW_RX

TX

(Data register) DR

Transmitter

clock

Receiver

clock

Receiver rate

Transmitter rate

f

PCLKx(x=1,2)

control

control

/

[8 x (2 - OVER8)]

Conventional baud rate generator

SBKRWURETE

IDLERXNE

TCIETXEIE

CR1

UE PCE PS

PEIE

PE

PWDATA

IRLP

SCEN

IREN

DMAR

DMAT

USART Address

CR2

CR3

IrDA

SIR

ENDEC

block

LINE

CKEN CPOL

CPHA LBCL

SCLK control

SCLK

CR2

GT

STOP[1:0]

NACK

DIV_Mantissa

15

0

RE

USART_BRR

/USARTDIV

TE

HD

(CPU or DMA)

(CPU or DMA)

PRDATA

Hardware

flow

controller

CTS LBD

RX

IRDA_OUT

IRDA_IN

nRTS

nCTS

GTPR

PSC

IE

IE

DIV_Fraction

4

USARTDIV = DIV_Mantissa + (DIV_Fraction / 8 × (2 – OVER8))

SAMPLING

CR1

OVER8

DIVIDER

ai16099

Loading...

Loading...