Embedded Flash memory interface RM0390

80/1328 RM0390 Rev 4

The OTP area is divided into 16 OTP data blocks of 32 bytes and one lock OTP block of 16

bytes. The OTP data and lock blocks cannot be erased. The lock block contains 16 bytes

LOCKBi (0 i 15) to lock the corresponding OTP data block (blocks 0 to 15). Each OTP

data block can be programmed until the value 0x00 is programmed in the corresponding

OTP lock byte. The lock bytes must only contain 0x00 and 0xFF values, otherwise the OTP

bytes might not be taken into account correctly.

3.8 Flash interface registers

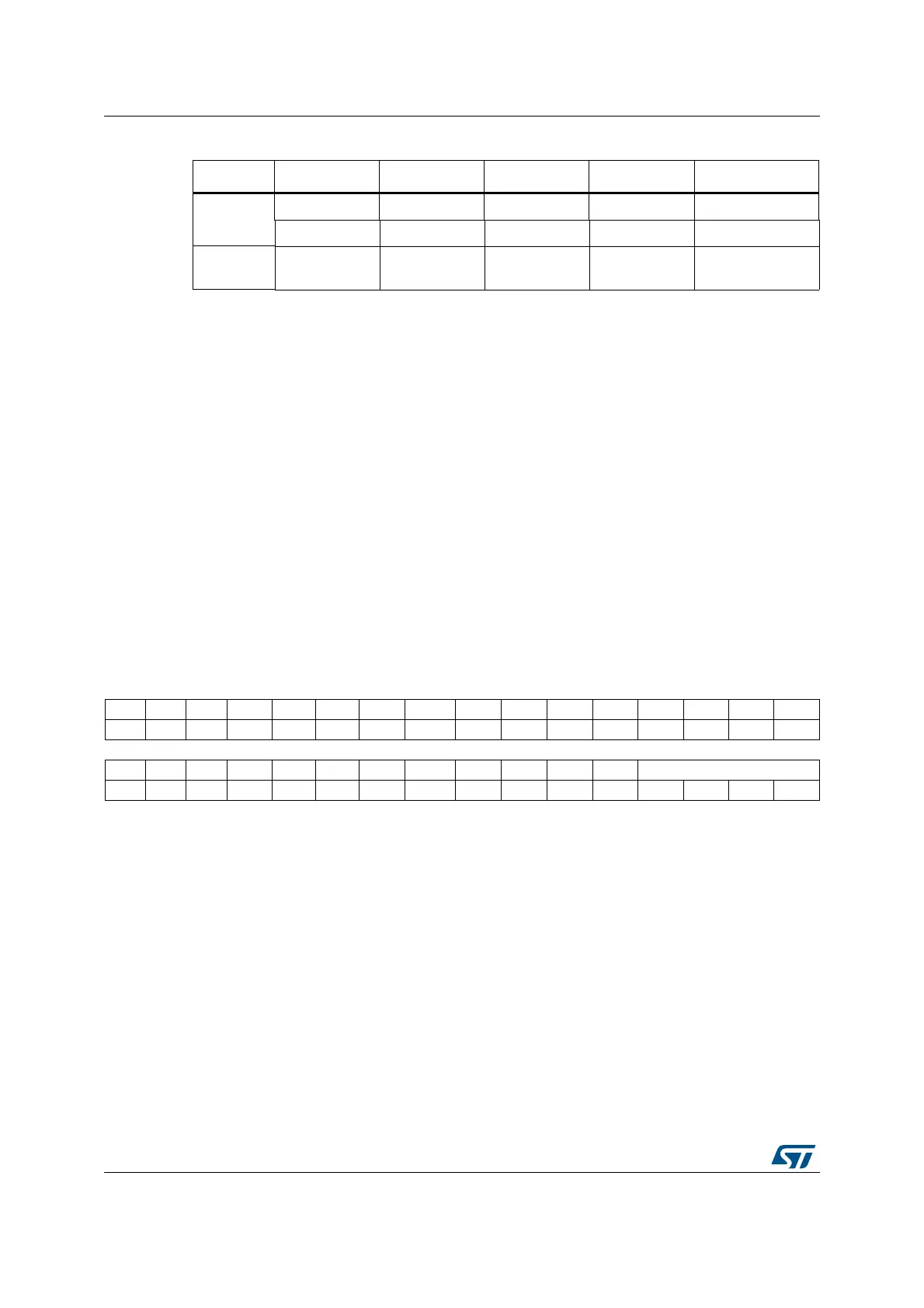

3.8.1 Flash access control register (FLASH_ACR)

The Flash access control register is used to enable/disable the acceleration features and

control the Flash memory access time according to CPU frequency.

Address offset: 0x00

Reset value: 0x0000 0000

Access: no wait state, word, half-word and byte access

15

OTP15 OTP15 OTP15 OTP15 0x1FFF 79E0

OTP15 OTP15 OTP15 OTP15 0x1FFF 79F0

Lock block

LOCKB15 ...

LOCKB12

LOCKB11 ...

LOCKB8

LOCKB7 ...

LOCKB4

LOCKB3 ...

LOCKB0

0x1FFF 7A00

Table 11. OTP area organization (continued)

Block [128:96] [95:64] [63:32] [31:0] Address byte 0

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. DCRST ICRST DCEN ICEN PRFTEN Res. Res. Res. Res. LATENCY

rwwrwrw rw rwrwrwrw

Bits 31:13 Reserved, must be kept cleared.

Bit 12 DCRST: Data cache reset

0: Data cache is not reset

1: Data cache is reset

This bit can be written only when the D cache is disabled.

Bit 11 ICRST: Instruction cache reset

0: Instruction cache is not reset

1: Instruction cache is reset

This bit can be written only when the I cache is disabled.

Bit 10 DCEN: Data cache enable

0: Data cache is disabled

1: Data cache is enabled

Loading...

Loading...