RM0390 Rev 4 687/1328

RM0390 Real-time clock (RTC)

691

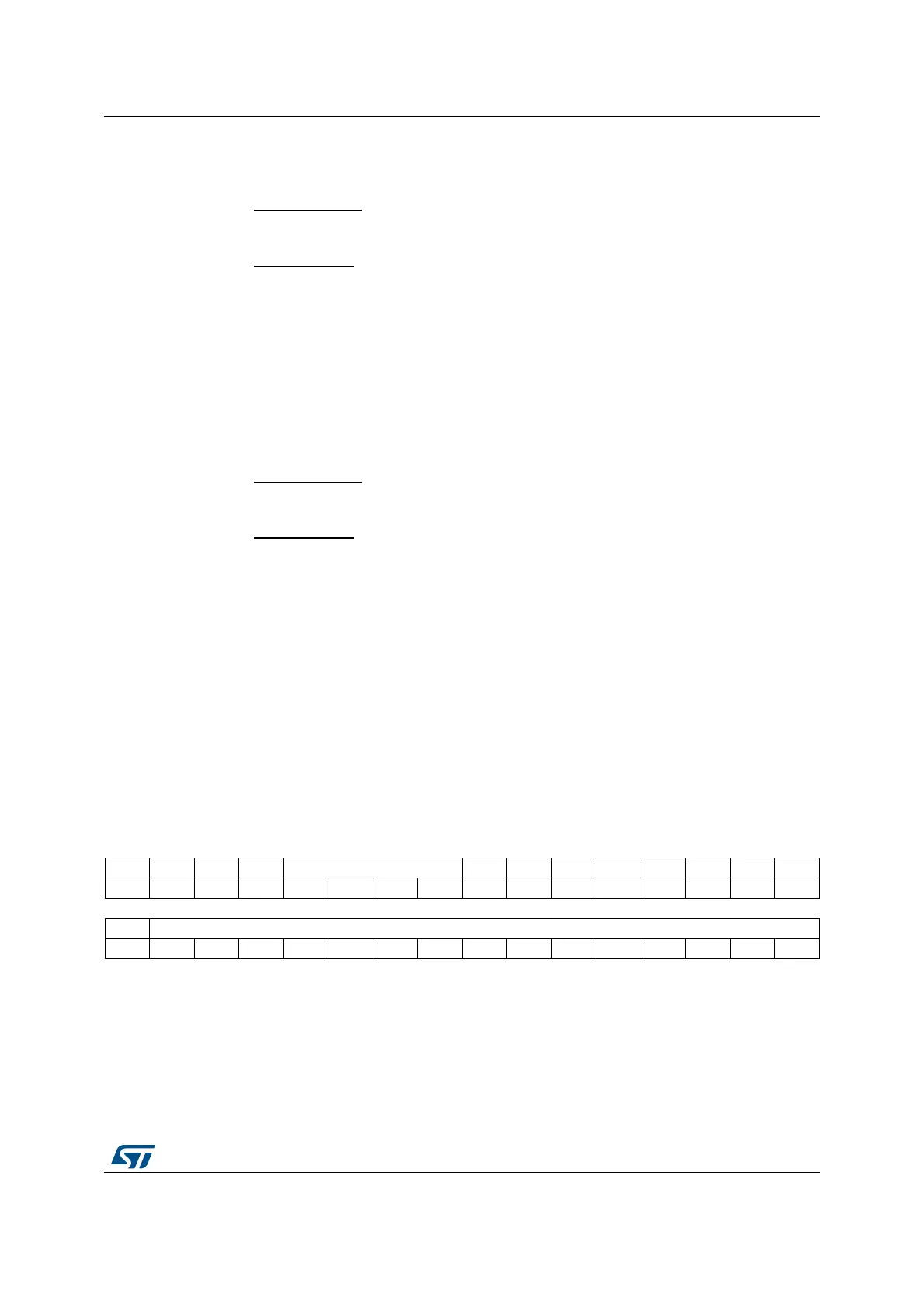

22.6.18 RTC alarm A sub second register (RTC_ALRMASSR)

Address offset: 0x44

Backup domain reset value: 0x0000 0000

System reset: not affected

Bits 6:5 Reserved. Always read as 0.

Bit 4 TAMP2TRG: Active level for tamper 2

if TAMPFLT != 00

0: TAMPER2 staying low triggers a tamper detection event.

1: TAMPER2 staying high triggers a tamper detection event.

if TAMPFLT = 00

:

0: TAMPER2 rising edge triggers a tamper detection event.

1: TAMPER2 falling edge triggers a tamper detection event.

Bit 3 TAMP2E: Tamper 2 detection enable

0: Tamper 2 detection disabled

1: Tamper 2 detection enabled

Bit 2 TAMPIE: Tamper interrupt enable

0: Tamper interrupt disabled

1: Tamper interrupt enabled

Bit 1 TAMP1TRG: Active level for tamper 1

if TAMPFLT != 00:

0: TAMPER1 staying low triggers a tamper detection event.

1: TAMPER1 staying high triggers a tamper detection event.

if TAMPFLT = 00

:

0: TAMPER1 rising edge triggers a tamper detection event.

1: TAMPER1 falling edge triggers a tamper detection event.

Caution: When TAMPFLT = 0, TAMP1E must be reset when TAMP1TRG is changed to avoid

spuriously setting TAMP1F.

Bit 0 TAMP1E: Tamper 1 detection enable

0: Tamper 1 detection disabled

1: Tamper 1 detection enabled

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. MASKSS[3:0] Res. Res. Res. Res. Res. Res. Res. Res.

rw rw rw rw

1514131211109876543210

Res. SS[14:0]

rw rw rw rw rw rw rw rw rw rw rw rw w rw rw

Loading...

Loading...