USB on-the-go full-speed/high-speed (OTG_FS/OTG_HS) RM0390

1118/1328 RM0390 Rev 4

31.15.4 OTG USB configuration register (OTG_GUSBCFG)

Address offset: 0x00C

Reset value: 0x0000 1440 for USB OTG FS

Reset value: 0x0000 1400 for USB OTG HS

This register can be used to configure the core after power-on or a changing to host mode

or device mode. It contains USB and USB-PHY related configuration parameters. The

application must program this register before starting any transactions on either the AHB or

the USB. Do not make changes to this register after the initial programming.

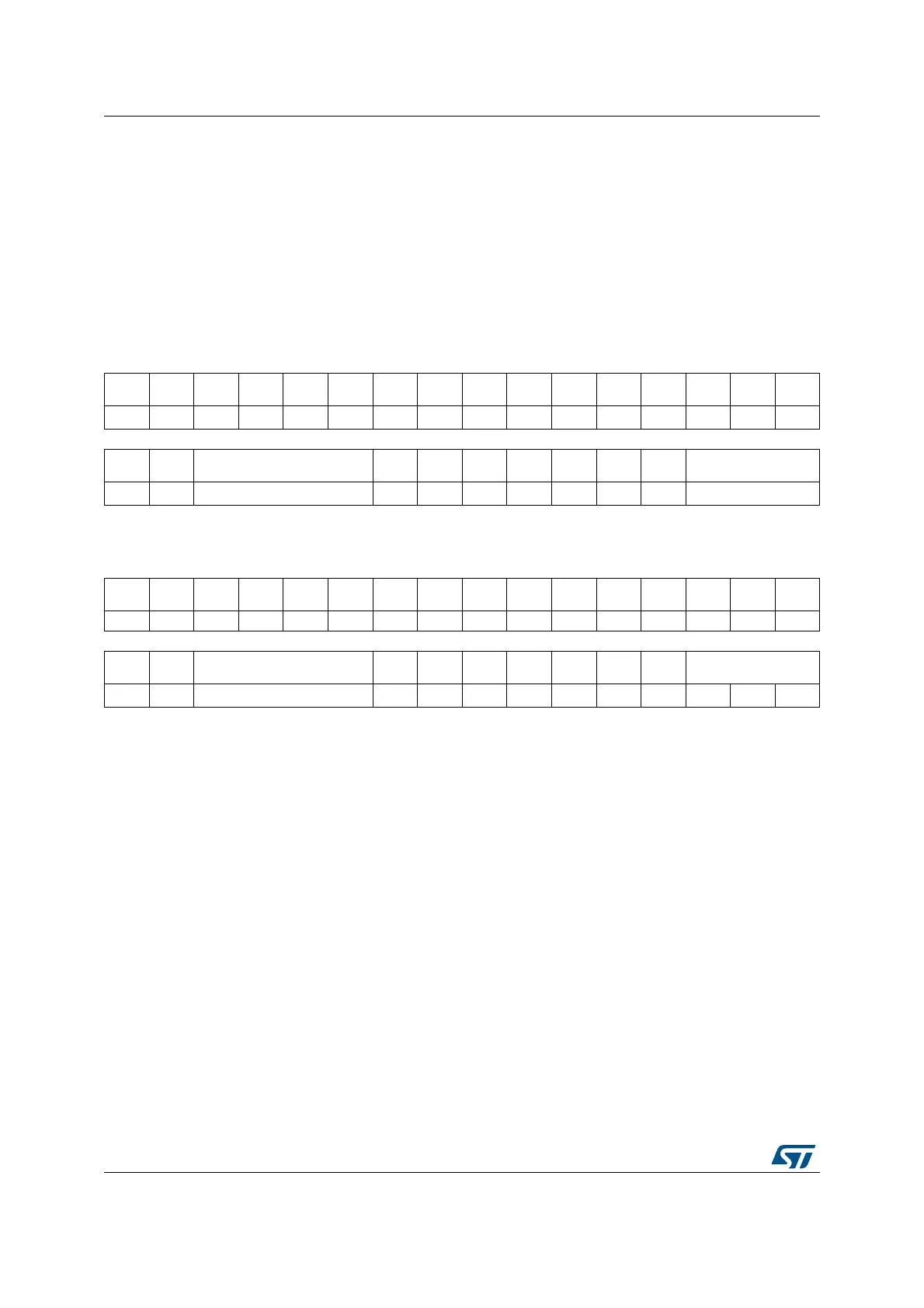

Note: Configuration register for USB OTG FS

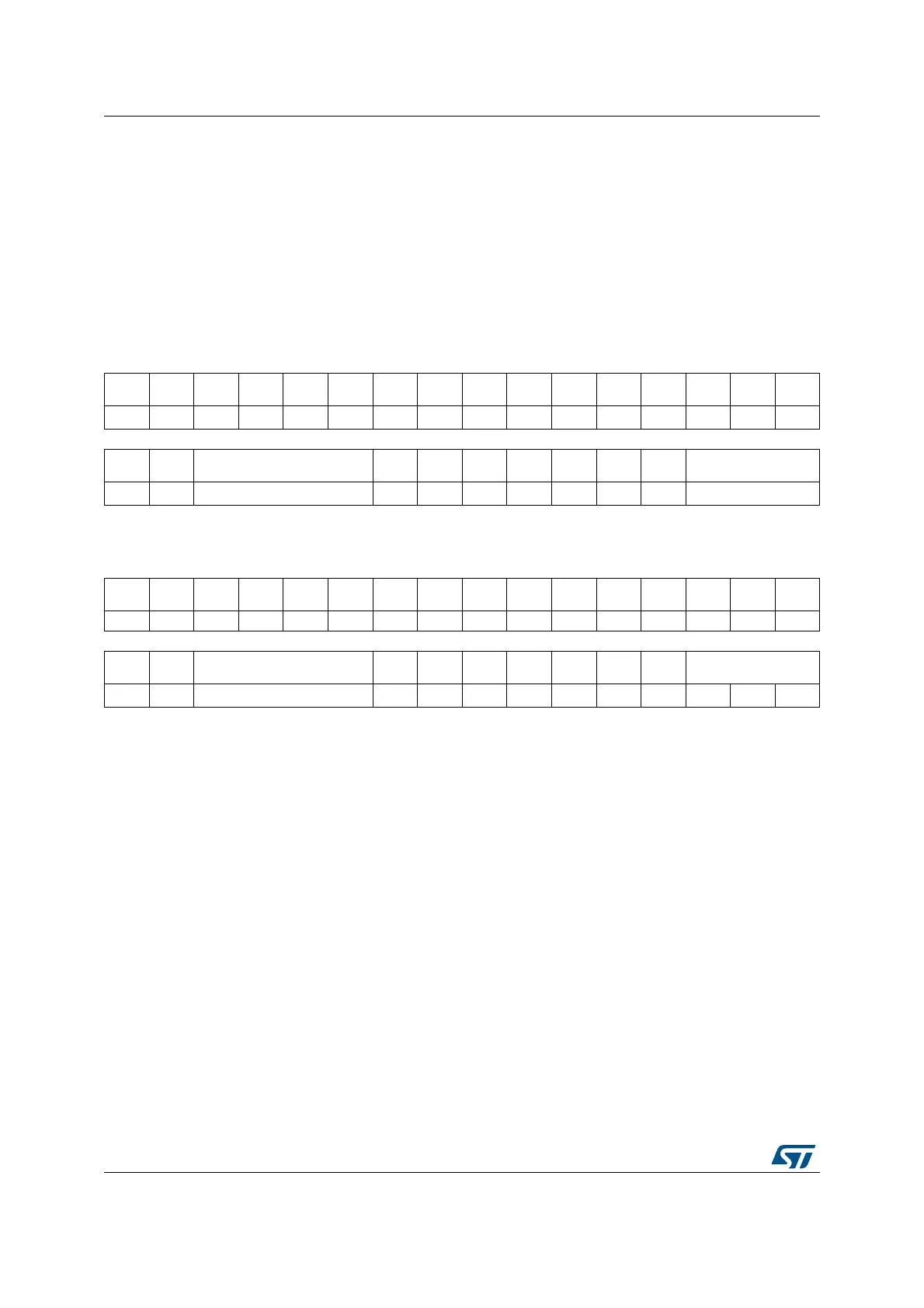

Note: Configuration register for USB OTG HS

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res.

FD

MOD

FH

MOD

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rw rw

1514131211109876543210

Res. Res. TRDT

HNP

CAP

SRP

CAP

Res.

PHY

SEL

Res. Res. Res. TOCAL

rw rw rw r rw

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res.

FD

MOD

FH

MOD

Res. Res. Res.

ULPI

IPD

PTCI PCCI TSDPS

ULPIE

VBUSI

ULPIE

VBUSD

ULPI

CSM

ULPI

AR

ULPI

FSL

Res.

rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

PHYL

PC

Res. TRDT[3:0]

HNP

CAP

SRP

CAP

Res.

PHY

SEL

Res. Res. Res. TOCAL[2:0]

rw rw rw rw rw rw rw rw

Bit 31 Reserved, must be kept at reset value.

Bit 30 FDMOD: Force device mode

Writing a 1 to this bit, forces the core to device mode irrespective of the OTG_ID input pin.

0: Normal mode

1: Force device mode

After setting the force bit, the application must wait at least 25 ms before the change takes

effect.

Note: Accessible in both device and host modes.

Bit 29 FHMOD: Force host mode

Writing a 1 to this bit, forces the core to host mode irrespective of the OTG_ID input pin.

0: Normal mode

1: Force host mode

After setting the force bit, the application must wait at least 25 ms before the change takes

effect.

Note: Accessible in both device and host modes.

Bits 28:26 Reserved, must be kept at reset value.

Loading...

Loading...