USB on-the-go full-speed/high-speed (OTG_FS/OTG_HS) RM0390

1122/1328 RM0390 Rev 4

Note: Configuration register for USB OTG HS

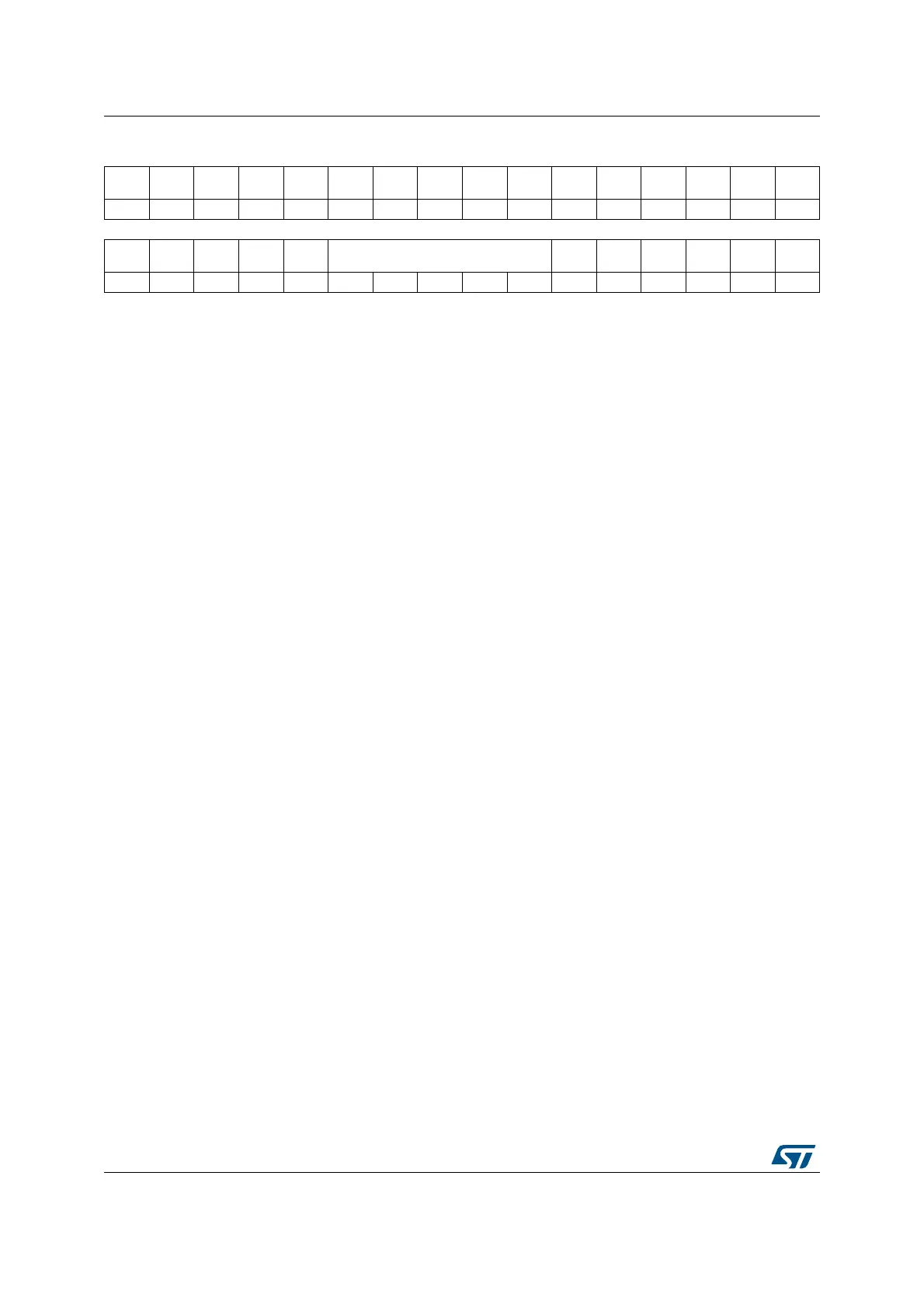

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

AHB

IDL

DMAR

EQ

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rr

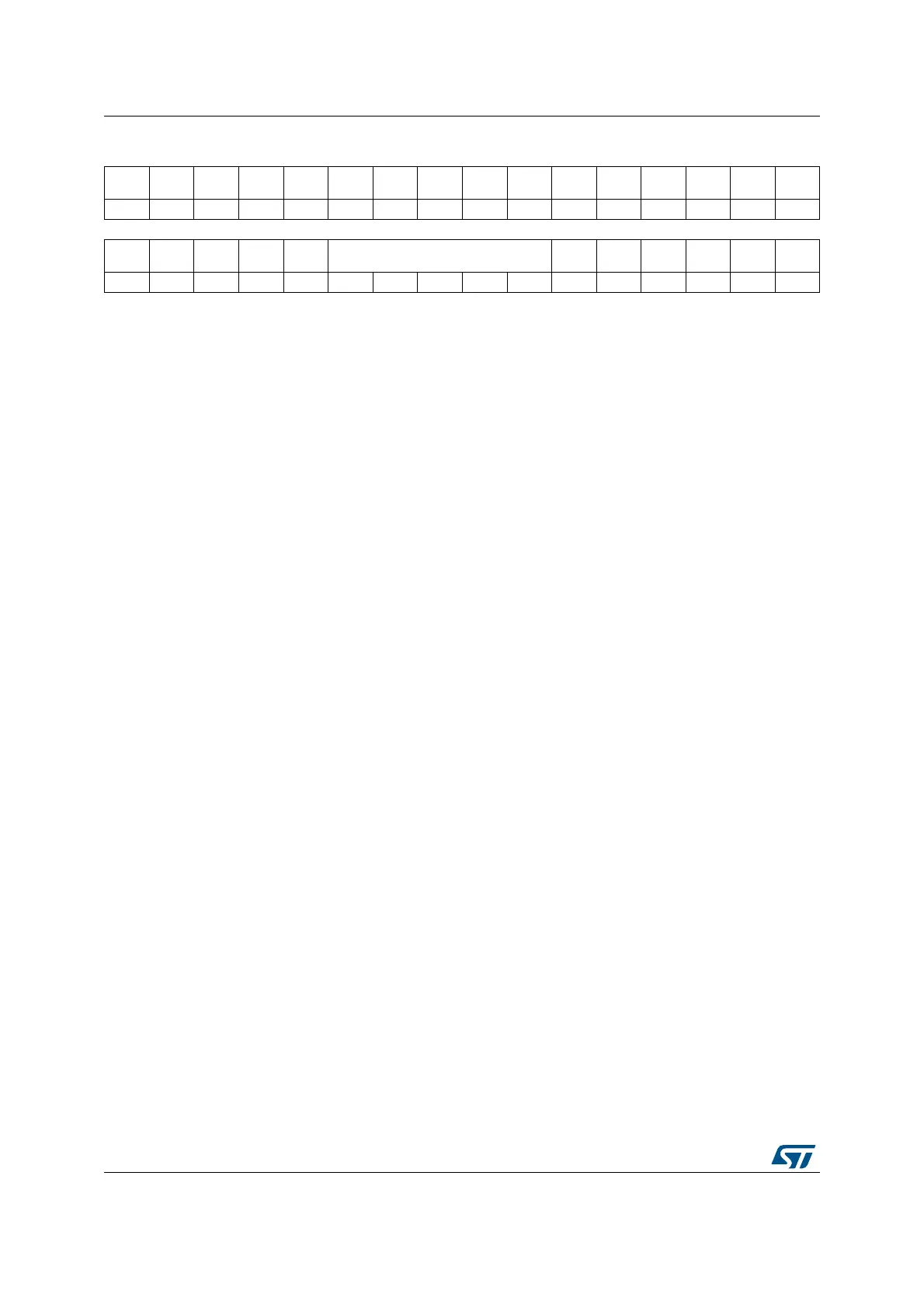

1514131211109876543210

Res. Res. Res. Res. Res. TXFNUM[4:0]

TXF

FLSH

RXF

FLSH

Res. Res. PSRST CSRST

rw rw rw rw rw rs rs rs rs

Bit 31 AHBIDL: AHB master idle

Indicates that the AHB master state machine is in the Idle condition.

Note: Accessible in both device and host modes.

Bits 30:11 Reserved, must be kept at reset value for USB OTG FS.

Bit 30 DMAREQ: DMA request signal enabled for USB OTG HS

This bit indicates that the DMA request is in progress. Used for debug.

Bits 29:11 Reserved, must be kept at reset value for USB OTG HS.

Bits 10:6 TXFNUM[4:0]: Tx FIFO number

This is the FIFO number that must be flushed using the Tx FIFO Flush bit. This field must not

be changed until the core clears the Tx FIFO Flush bit.

00000:

– Non-periodic Tx FIFO flush in host mode

– Tx FIFO 0 flush in device mode

00001:

– Periodic Tx FIFO flush in host mode

– Tx FIFO 1 flush in device mode

00010: Tx FIFO 2 flush in device mode

...

01111: Tx FIFO 15 flush in device mode

10000: Flush all the transmit FIFOs in device or host mode.

Note: Accessible in both device and host modes.

Bit 5 TXFFLSH: Tx FIFO flush

This bit selectively flushes a single or all transmit FIFOs, but cannot do so if the core is in the

midst of a transaction.

The application must write this bit only after checking that the core is neither writing to the Tx

FIFO nor reading from the Tx FIFO. Verify using these registers:

Read—NAK Effective interrupt ensures the core is not reading from the FIFO

Write—AHBIDL bit in OTG_GRSTCTL ensures the core is not writing anything to the FIFO.

Flushing is normally recommended when FIFOs are reconfigured. FIFO flushing is also

recommended during device endpoint disable. The application must wait until the core clears

this bit before performing any operations. This bit takes eight clocks to clear, using the slower

clock of phy_clk or hclk.

Note: Accessible in both device and host modes.

Loading...

Loading...