USB on-the-go full-speed/high-speed (OTG_FS/OTG_HS) RM0390

1184/1328 RM0390 Rev 4

Note: Configuration register for USB OTG HS.

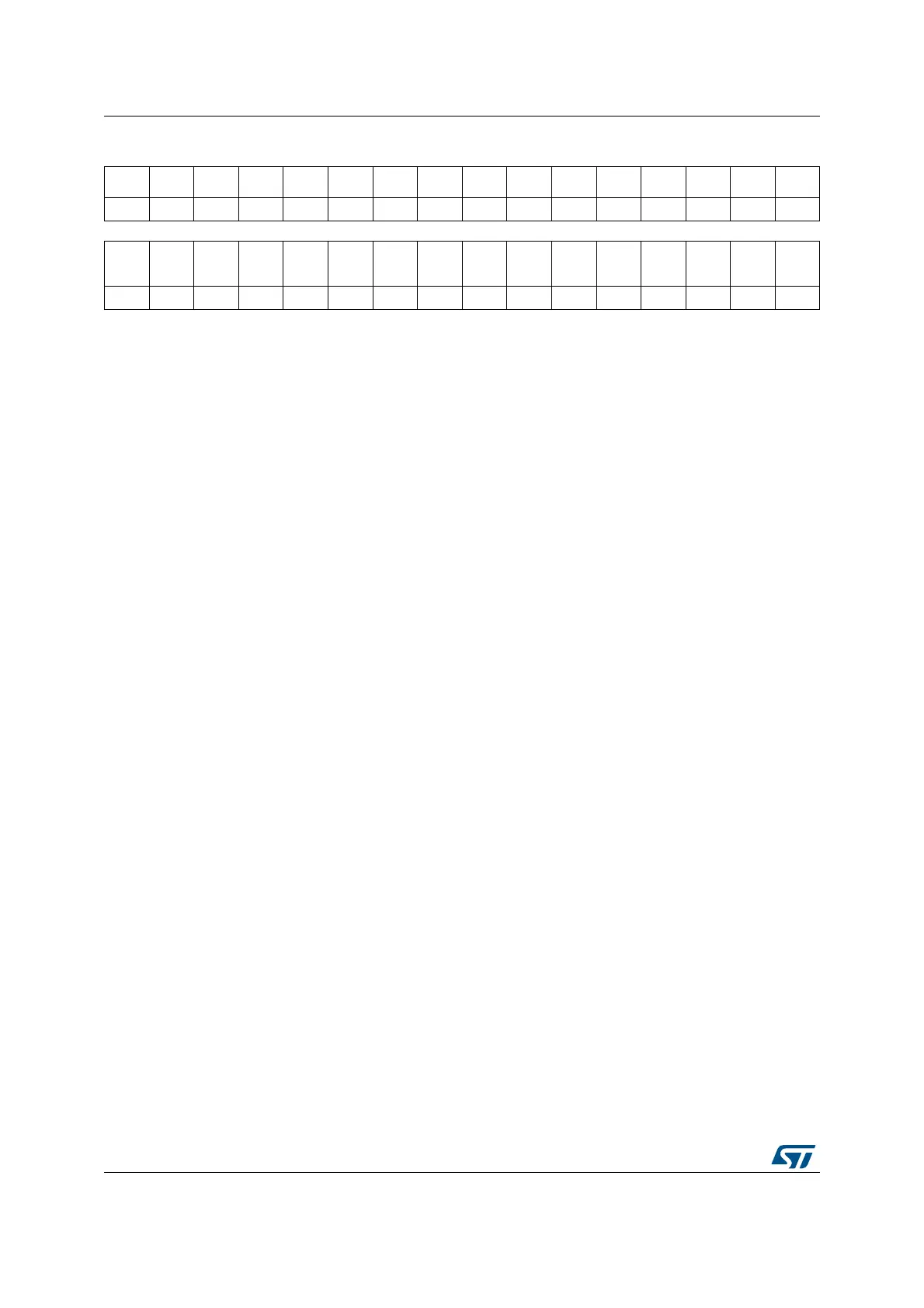

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

STPK

TRX

NYET NAK BERR Res. Res. Res.

OUT

PKT

ERR

Res.

B2B

STUP

STSPH

SRX

OTEP

DIS

STUP

AHB

ERR

EP

DISD

XFRC

rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1

rc_w1

rc_w1rc_w1rc_w1rc_w1rc_w1

Bits 31:16 Reserved, must be kept at reset value.

Bit 15 STPKTRX: Setup packet received.

Applicable for control OUT endpoints in only in the Buffer DMA Mode. Set by the OTG_HS,

this bit indicates that this buffer holds 8 bytes of setup data. There is only one setup packet

per buffer. On receiving a setup packet, the OTG_HS closes the buffer and disables the

corresponding endpoint after SETUP_COMPLETE status is seen in the Rx FIFO. OTG_HS

puts a SETUP_COMPLETE status into the Rx FIFO when it sees the first IN or OUT token

after the SETUP packet for that particular endpoint. The application must then re-enable the

endpoint to receive any OUT data for the control transfer and reprogram the buffer start

address. Because of the above behavior, OTG_HS can receive any number of back to back

setup packets and one buffer for every setup packet is used.

Bit 14 NYET: NYET interrupt

This interrupt is generated when a NYET response is transmitted for a non isochronous

OUT endpoint.

Bit 13 NAK: NAK input

The core generates this interrupt when a NAK is transmitted or received by the device. In

case of isochronous IN endpoints the interrupt gets generated when a zero length packet is

transmitted due to unavailability of data in the Tx FIFO.

Bit 12 BERR: Babble error interrupt

The core generates this interrupt when babble is received for the endpoint.

Bits 11:10 Reserved, must be kept at reset value.

Bit 9 Reserved, must be kept at reset value.

Bit 8 OUTPKTERR: OUT packet error

This interrupt is asserted when the core detects an overflow or a CRC error for an OUT

packet. This interrupt is valid only when thresholding is enabled.

Bit 7 Reserved, must be kept at reset value.

Bit 6 B2BSTUP: Back-to-back SETUP packets received for USB OTG HS

Applies to control OUT endpoint only.

This bit indicates that the core has received more than three back-to-back SETUP packets

for this particular endpoint.

Bit 5 STSPHSRX: Status phase received for control write

This interrupt is valid only for control OUT endpoints. This interrupt is generated only after

OTG_FS/OTG_HS has transferred all the data that the host has sent during the data phase

of a control write transfer, to the system memory buffer. The interrupt indicates to the

application that the host has switched from data phase to the status phase of a control write

transfer. The application can use this interrupt to ACK or STALL the status phase, after it has

decoded the data phase.

Loading...

Loading...