RM0390 Rev 4 303/1328

RM0390 Flexible memory controller (FMC)

324

Attribute memory space timing registers (FMC_PATT)

Address offset: 0x8C

Reset value: 0xFCFC FCFC

The FMC_PATT read/write register contains the timing information for NAND Flash memory

bank. It is used for 8-bit accesses to the attribute memory space of the NAND Flash for the

last address write access if the timing must differ from that of previous accesses (for

Ready/Busy management, refer to Section 11.6.5: NAND Flash prewait functionality).

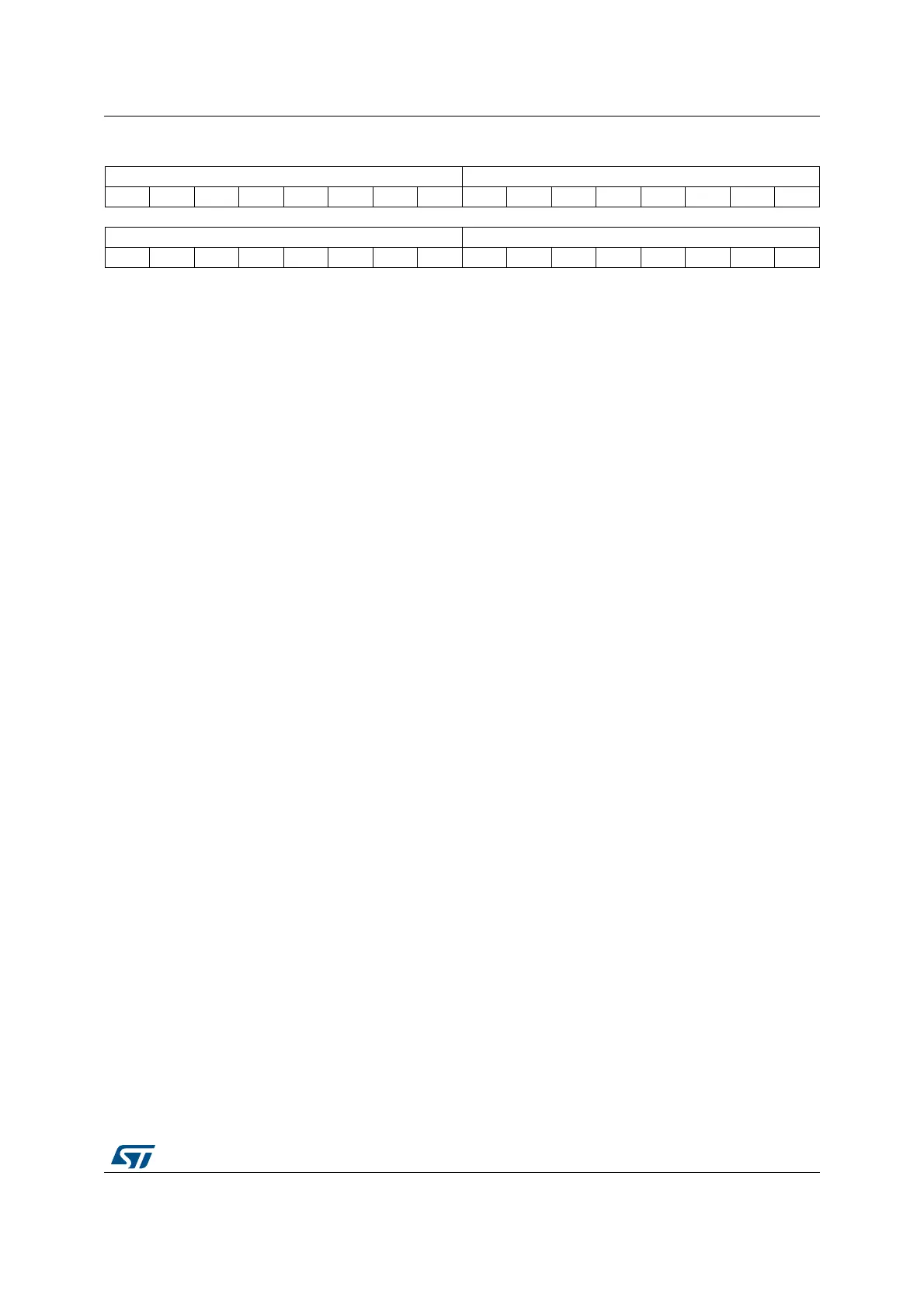

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

MEMHIZx MEMHOLDx

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

MEMWAITx MEMSETx

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:24 MEMHIZ[7:0]: Common memory x data bus Hi-Z time

Defines the number of HCLK clock cycles during which the data bus is kept Hi-Z after the

start of a NAND Flash write access to common memory space on socket. This is only valid

for write transactions:

0000 0000: 1 HCLK cycle

1111 1110: 255 HCLK cycles

1111 1111: reserved.

Bits 23:16 MEMHOLD[7:0]: Common memory hold time

Defines the number of HCLK clock cycles for write access and HCLK (+2) clock cycles for

read access during which the address is held (and data for write accesses) after the

command is deasserted (NWE, NOE), for NAND Flash read or write access to common

memory space on socket x:

0000 0000: reserved.

0000 0001: 1 HCLK cycle for write access / 3 HCLK cycles for read access

1111 1110: 254 HCLK cycles for write access / 256 HCLK cycles for read access

1111 1111: reserved.

Bits 15:8 MEMWAIT[7:0]: Common memory wait time

Defines the minimum number of HCLK (+1) clock cycles to assert the command (NWE,

NOE), for NAND Flash read or write access to common memory space on socket. The

duration of command assertion is extended if the wait signal (NWAIT) is active (low) at the

end of the programmed value of HCLK:

0000 0000: reserved

0000 0001: 2HCLK cycles (+ wait cycle introduced by deasserting NWAIT)

1111 1110: 255 HCLK cycles (+ wait cycle introduced by deasserting NWAIT)

1111 1111: reserved.

Bits 7:0 MEMSET[7:0]: Common memory x setup time

Defines the number of HCLK (+1) clock cycles to set up the address before the command

assertion (NWE, NOE), for NAND Flash read or write access to common memory space on

socket x:

0000 0000: 1 HCLK cycle

1111 1110: 255 HCLK cycles

1111 1111: reserved

Loading...

Loading...