RM0390 Rev 4 321/1328

RM0390 Flexible memory controller (FMC)

324

As soon as the FMC_SDRTR register is programmed, the timer starts counting. If the value

programmed in the register is ’0’, no refresh is carried out. This register must not be

reprogrammed after the initialization procedure to avoid modifying the refresh rate.

Each time a refresh pulse is generated, this 13-bit COUNT field is reloaded into the counter.

If a memory access is in progress, the Auto-refresh request is delayed. However, if the

memory access and Auto-refresh requests are generated simultaneously, the Auto-refresh

takes precedence. If the memory access occurs during a refresh operation, the request is

buffered to be processed when the refresh is complete.

This register is common to SDRAM bank 1 and bank 2.

Note: The programmed COUNT value must not be equal to the sum of the following timings:

TWR+TRP+TRC+TRCD+4 memory clock cycles .

SDRAM Status register (FMC_SDSR)

Address offset: 0x158

Reset value: 0x0000 0000

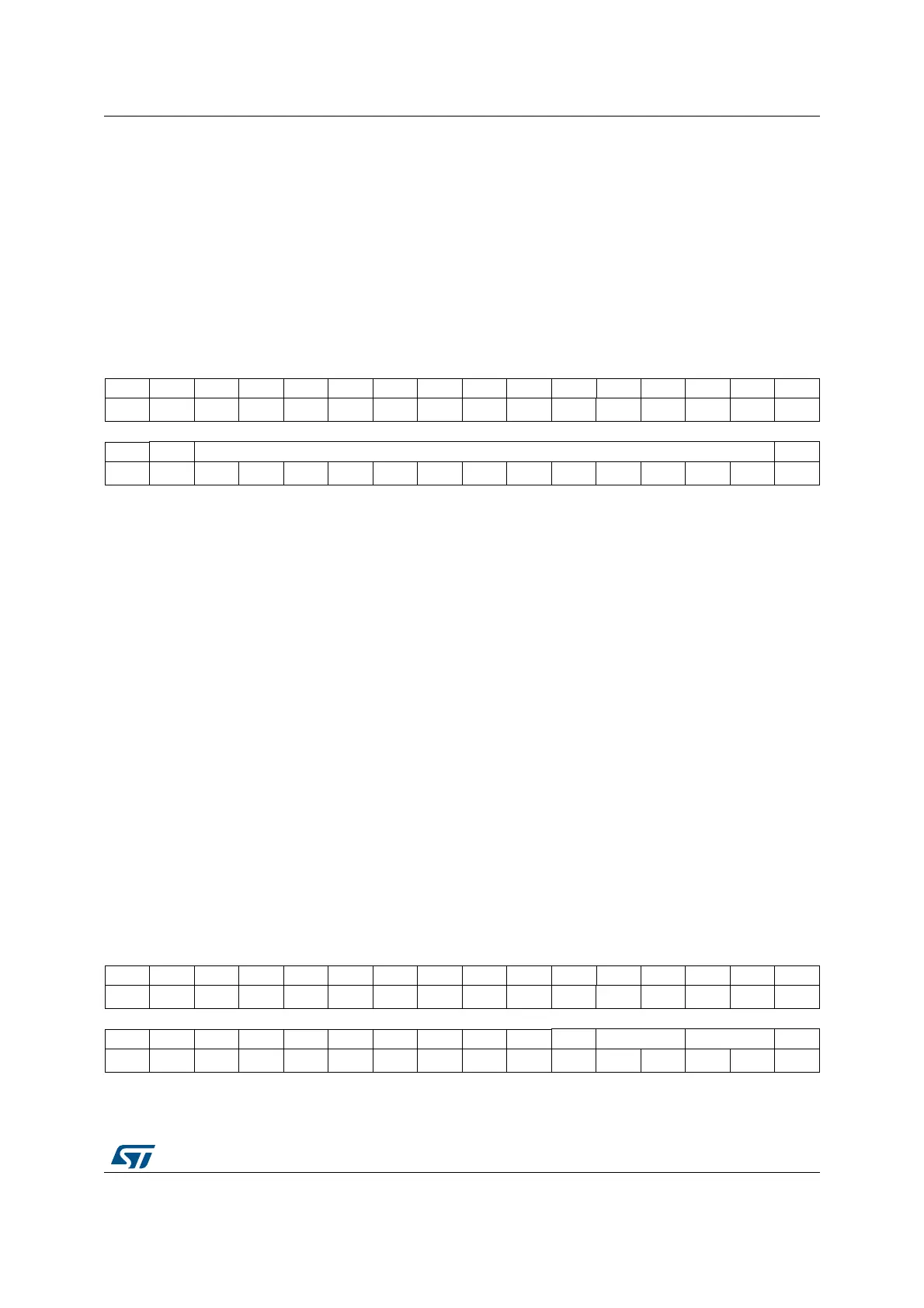

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. REIE COUNT CRE

rw rw rw rw rw rw rw rw rw rw rw rw rw rw w

Bits 31: 15 Reserved, must be kept at reset value

Bit 14 REIE: RES Interrupt Enable

0: Interrupt is disabled

1: An Interrupt is generated if RE = 1

Bits 13:1 COUNT[12:0]: Refresh Timer Count

This 13-bit field defines the refresh rate of the SDRAM device. It is expressed in number of memory

clock cycles. It must be set at least to 41 SDRAM clock cycles (0x29).

Refresh rate = (COUNT + 1) x SDRAM frequency clock

COUNT = (SDRAM refresh period / Number of rows) - 20

Bit 0 CRE: Clear Refresh error flag

This bit is used to clear the Refresh Error Flag (RE) in the Status Register.

0: no effect

1: Refresh Error flag is cleared

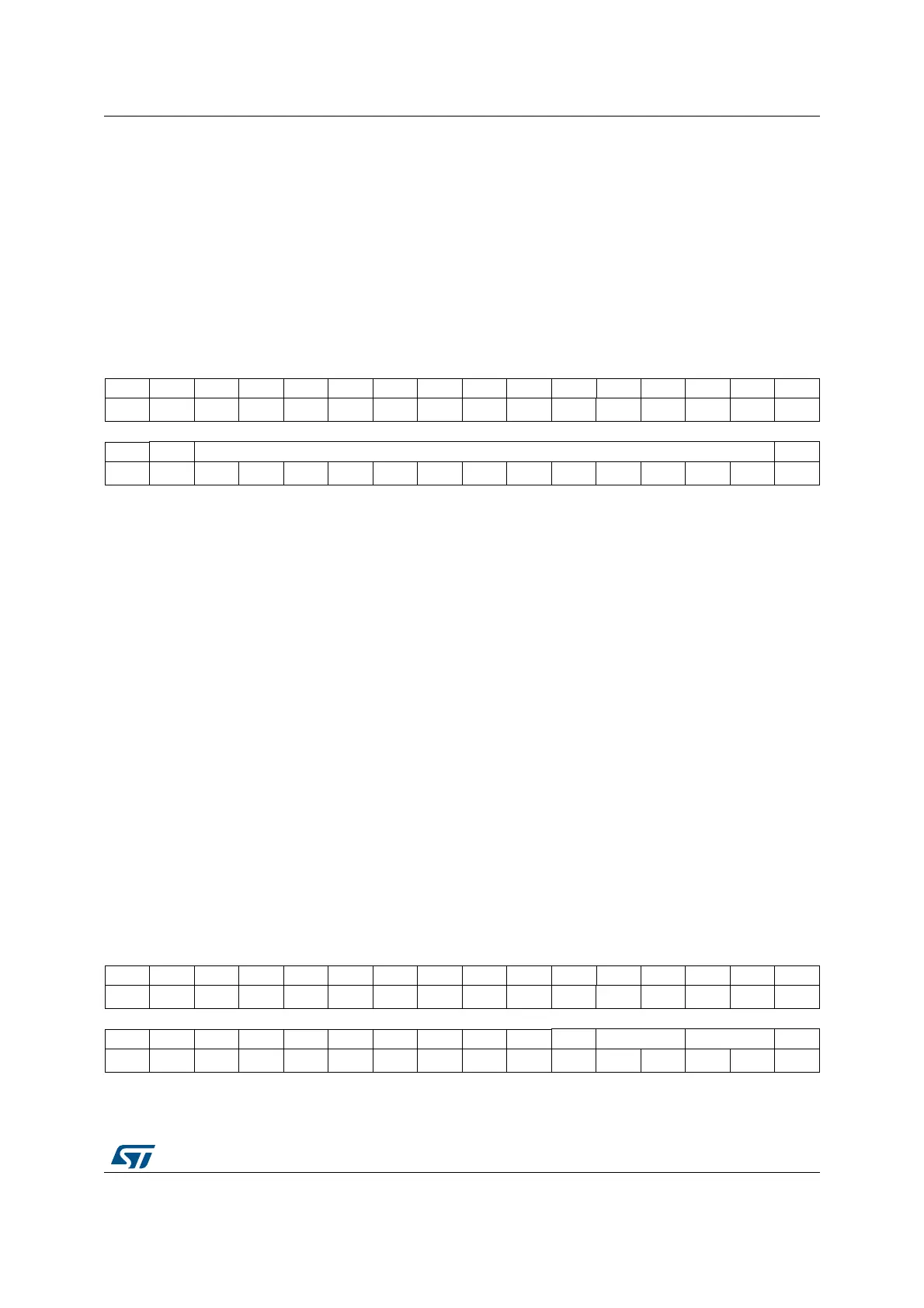

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. BUSY MODES2 MODES1 RE

rrrrrr

Bits 31:5 Reserved, must be kept at reset value

Loading...

Loading...