RM0453 Rev 1 1377/1461

RM0453 Debug support (DBG)

1448

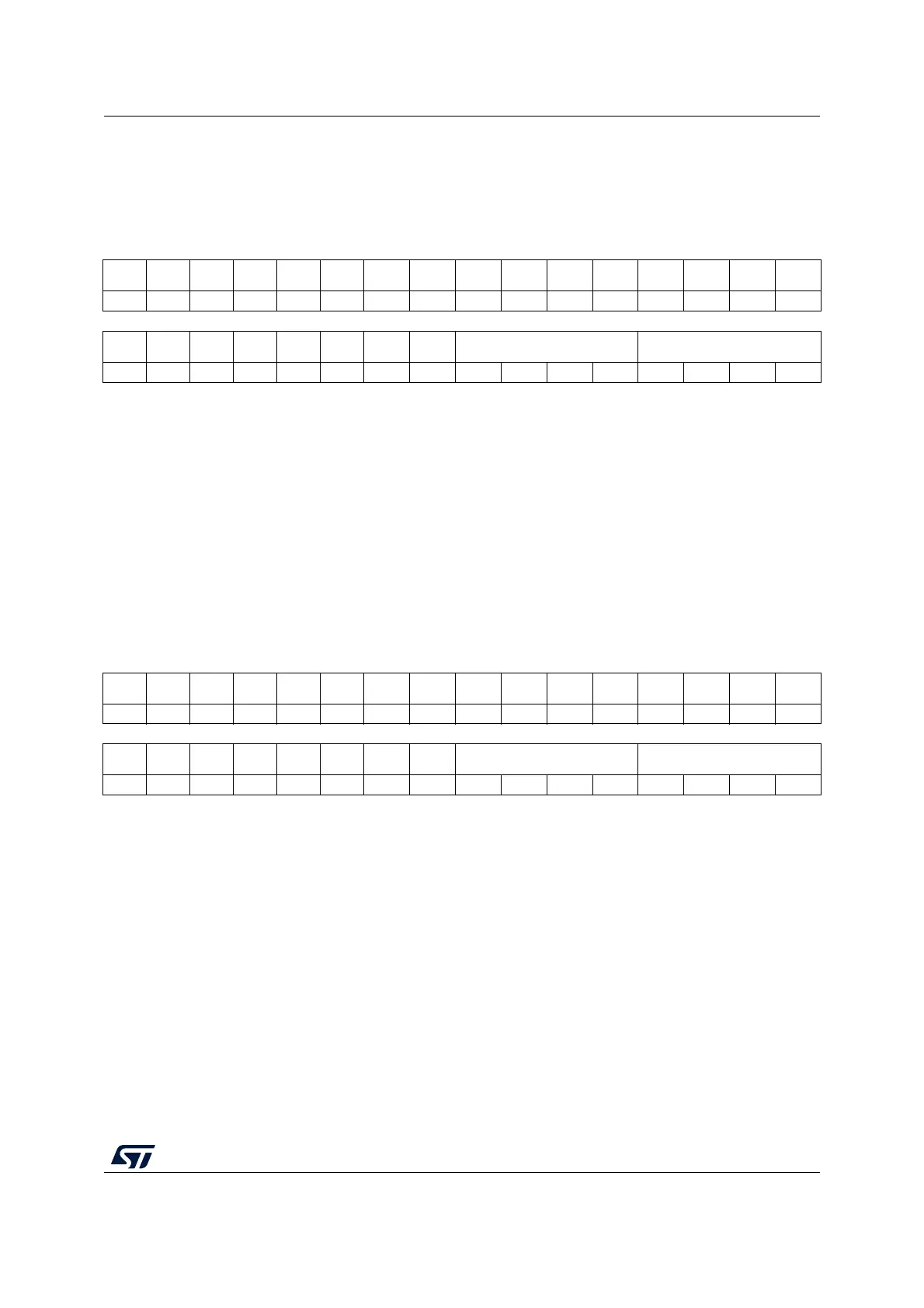

CTI device type identifier register (CTI_DEVTYPER)

Address offset: 0xFCC

Reset value: 0x0000 0014

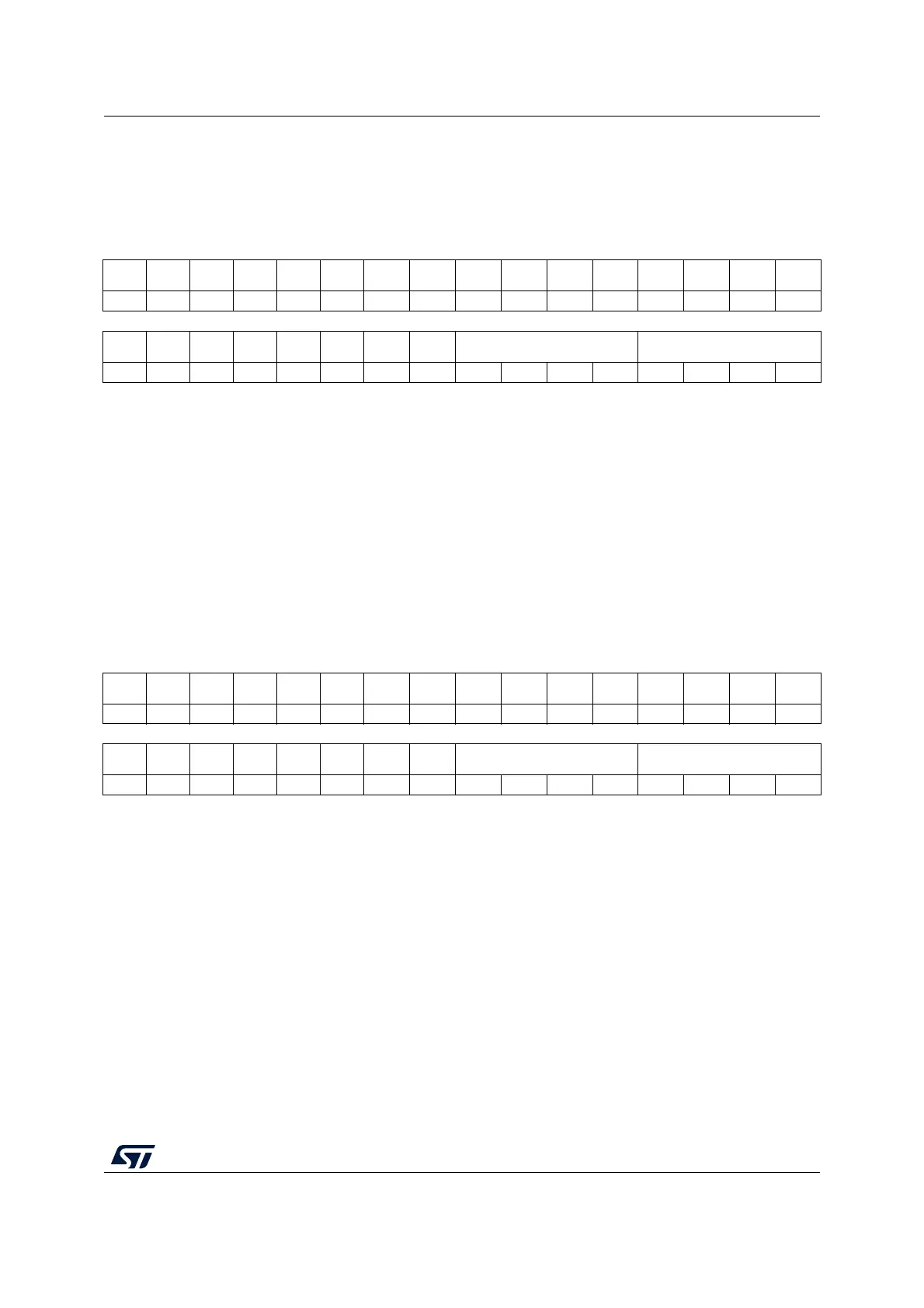

CTI CoreSight peripheral identity register 4 (CTI_PIDR4)

Address offset: 0xFD0

Reset value: 0x0000 0004

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. SUBTYPE[3:0] MAJORTYPE[3:0]

rrrrrrrr

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:4 SUBTYPE[3:0]: sub-classification

0x1: Indicates that this component is a cross-triggering component.

Bits 3:0 MAJORTYPE[3:0]: major classification

0x4: Indicates that this component allows a debugger to control other components in a

CoreSight™ SoC-400 system.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. F4KCOUNT[3:0] JEP106CON[3:0]

rrrrrrrr

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:4 F4KCOUNT[3:0]: register file size

0x0: The register file occupies a single 4-Kbyte region

Bits 3:0 JEP106CON[3:0]: JEP106 continuation code

0x4: Arm

®

JEDEC code

Loading...

Loading...