RM0390 Rev 4 1055/1328

RM0390 Controller area network (bxCAN)

1076

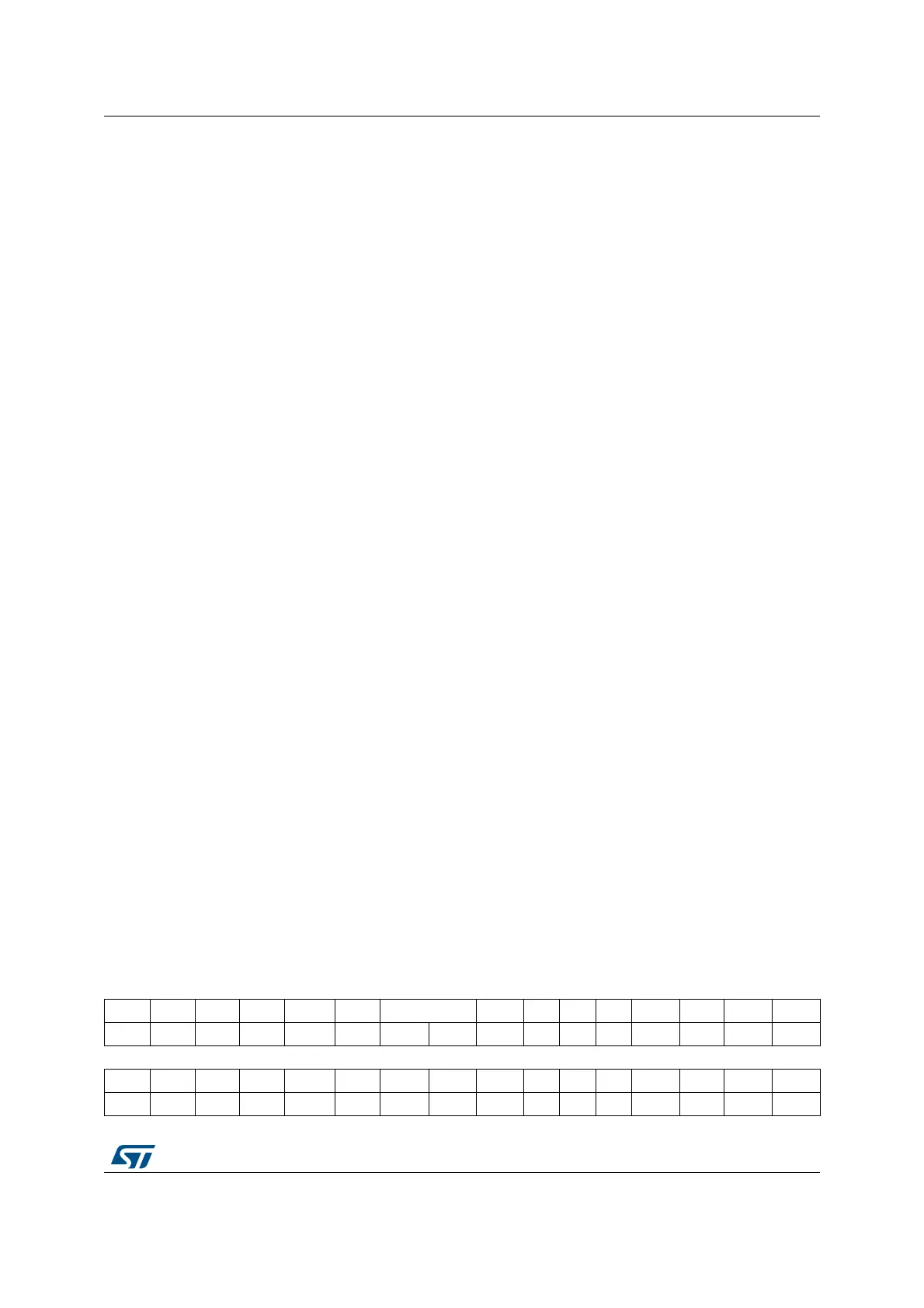

CAN transmit status register (CAN_TSR)

Address offset: 0x08

Reset value: 0x1C00 0000

Bit 8 TXM: Transmit mode

The CAN hardware is currently transmitter.

Bits 7:5 Reserved, must be kept at reset value.

Bit 4 SLAKI: Sleep acknowledge interrupt

When SLKIE=1, this bit is set by hardware to signal that the bxCAN has entered Sleep

Mode. When set, this bit generates a status change interrupt if the SLKIE bit in the

CAN_IER register is set.

This bit is cleared by software or by hardware, when SLAK is cleared.

Note: When SLKIE=0, no polling on SLAKI is possible. In this case the SLAK bit can be

polled.

Bit 3 WKUI

: Wakeup interrupt

This bit is set by hardware to signal that a SOF bit has been detected while the CAN

hardware was in Sleep mode. Setting this bit generates a status change interrupt if the

WKUIE bit in the CAN_IER register is set.

This bit is cleared by software.

Bit 2 ERRI

: Error interrupt

This bit is set by hardware when a bit of the CAN_ESR has been set on error detection and

the corresponding interrupt in the CAN_IER is enabled. Setting this bit generates a status

change interrupt if the ERRIE bit in the CAN_IER register is set.

This bit is cleared by software.

Bit 1 SLAK

: Sleep acknowledge

This bit is set by hardware and indicates to the software that the CAN hardware is now in

Sleep mode. This bit acknowledges the Sleep mode request from the software (set SLEEP

bit in CAN_MCR register).

This bit is cleared by hardware when the CAN hardware has left Sleep mode (to be

synchronized on the CAN bus). To be synchronized the hardware has to monitor a

sequence of 11 consecutive recessive bits on the CAN RX signal.

Note: The process of leaving Sleep mode is triggered when the SLEEP bit in the CAN_MCR

register is cleared. Refer to the AWUM bit of the CAN_MCR register description for

detailed information for clearing SLEEP bit

Bit 0 INAK

: Initialization acknowledge

This bit is set by hardware and indicates to the software that the CAN hardware is now in

initialization mode. This bit acknowledges the initialization request from the software (set

INRQ bit in CAN_MCR register).

This bit is cleared by hardware when the CAN hardware has left the initialization mode (to

be synchronized on the CAN bus). To be synchronized the hardware has to monitor a

sequence of 11 consecutive recessive bits on the CAN RX signal.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

LOW2 LOW1 LOW0 TME2 TME1 TME0 CODE[1:0] ABRQ2 Res. Res. Res. TERR2 ALST2 TXOK2 RQCP2

r r r r r r r r rs rc_w1 rc_w1 rc_w1 rc_w1

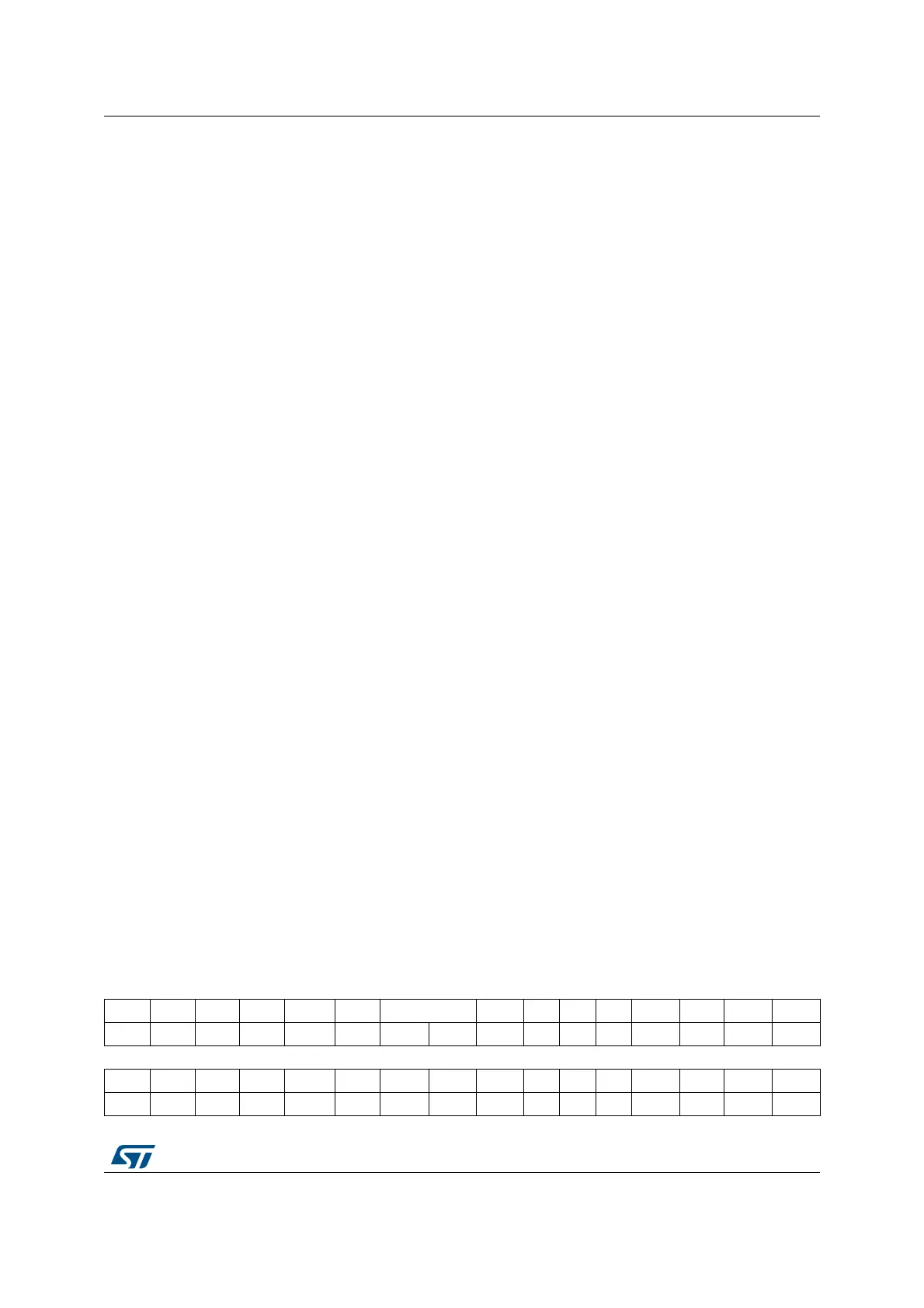

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

ABRQ1 Res. Res. Res. TERR1 ALST1 TXOK1 RQCP1 ABRQ0 Res. Res. Res. TERR0 ALST0 TXOK0 RQCP0

rs rc_w1 rc_w1 rc_w1 rc_w1 rs rc_w1 rc_w1 rc_w1 rc_w1

Loading...

Loading...