Controller area network (bxCAN) RM0390

1054/1328 RM0390 Rev 4

CAN master status register (CAN_MSR)

Address offset: 0x04

Reset value: 0x0000 0C02

Bit 3 RFLM: Receive FIFO locked mode

0: Receive FIFO not locked on overrun. Once a receive FIFO is full the next incoming

message will overwrite the previous one.

1: Receive FIFO locked against overrun. Once a receive FIFO is full the next incoming

message will be discarded.

Bit 2 TXFP: Transmit FIFO priority

This bit controls the transmission order when several mailboxes are pending at the same

time.

0: Priority driven by the identifier of the message

1: Priority driven by the request order (chronologically)

Bit 1 SLEEP

: Sleep mode request

This bit is set by software to request the CAN hardware to enter the Sleep mode. Sleep

mode will be entered as soon as the current CAN activity (transmission or reception of a

CAN frame) has been completed.

This bit is cleared by software to exit Sleep mode.

This bit is cleared by hardware when the AWUM bit is set and a SOF bit is detected on the

CAN Rx signal.

This bit is set after reset - CAN starts in Sleep mode.

Bit 0 INRQ

: Initialization request

The software clears this bit to switch the hardware into normal mode. Once 11 consecutive

recessive bits have been monitored on the Rx signal the CAN hardware is synchronized and

ready for transmission and reception. Hardware signals this event by clearing the INAK bit in

the CAN_MSR register.

Software sets this bit to request the CAN hardware to enter initialization mode. Once

software has set the INRQ bit, the CAN hardware waits until the current CAN activity

(transmission or reception) is completed before entering the initialization mode. Hardware

signals this event by setting the INAK bit in the CAN_MSR register.

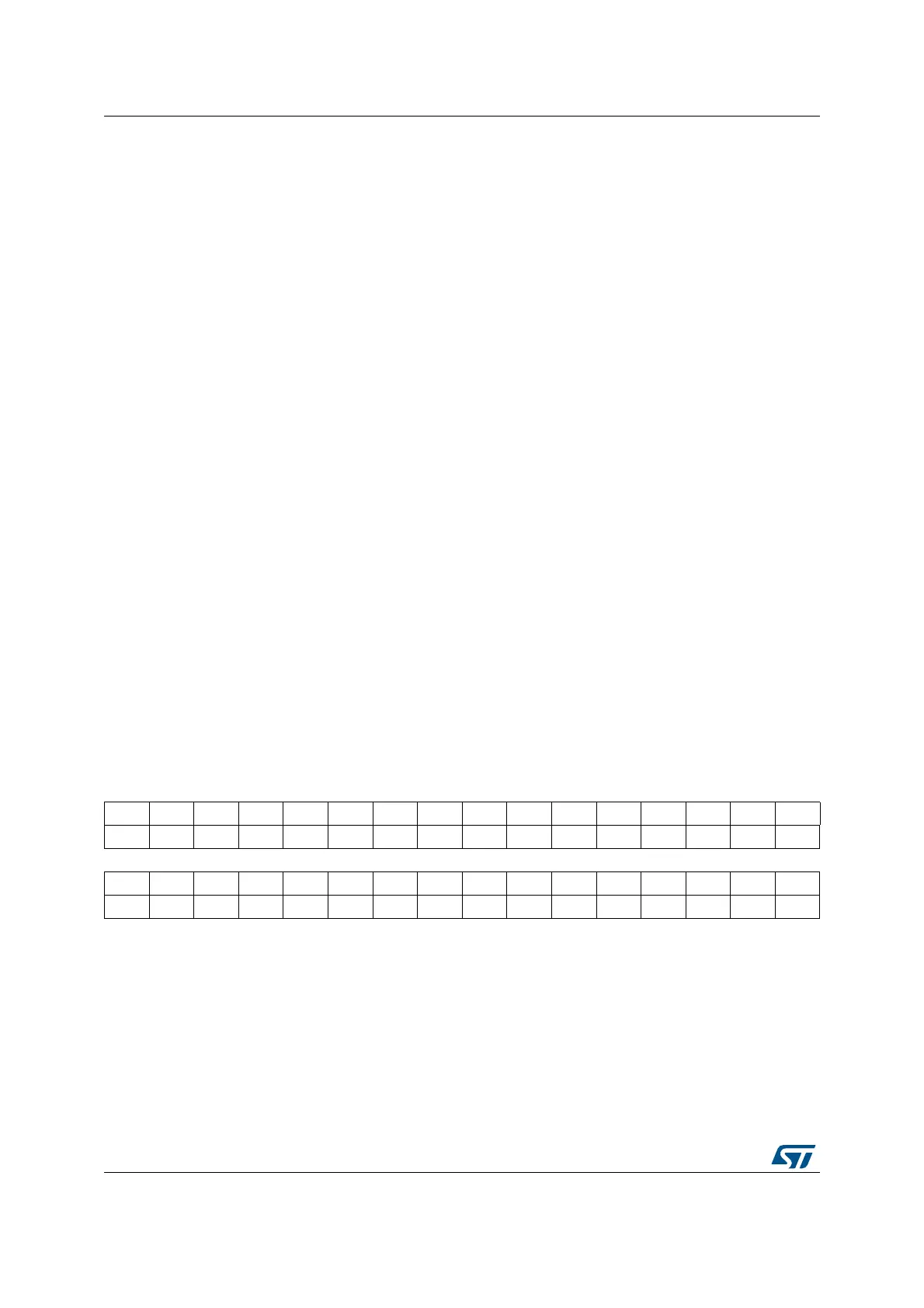

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. RX SAMP RXM TXM Res. Res. Res. SLAKI WKUI ERRI SLAK INAK

rrrr rc_w1rc_w1rc_w1rr

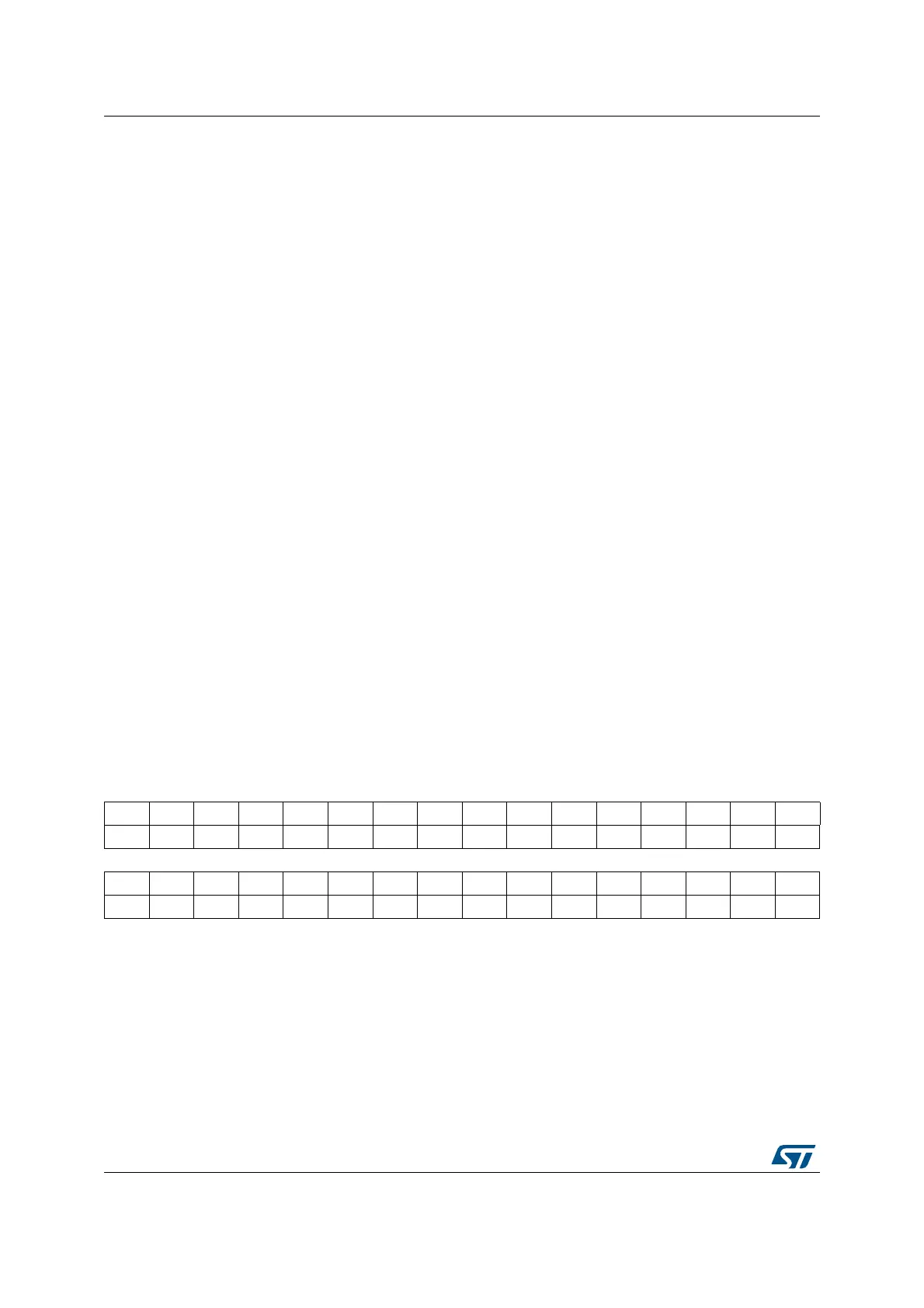

Bits 31:12 Reserved, must be kept at reset value.

Bit 11 RX

: CAN Rx signal

Monitors the actual value of the CAN_RX Pin.

Bit 10 SAMP

: Last sample point

The value of RX on the last sample point (current received bit value).

Bit 9 RXM

: Receive mode

The CAN hardware is currently receiver.

Loading...

Loading...