USB on-the-go full-speed/high-speed (OTG_FS/OTG_HS) RM0390

1178/1328 RM0390 Rev 4

Note: Configuration register for USB OTG HS

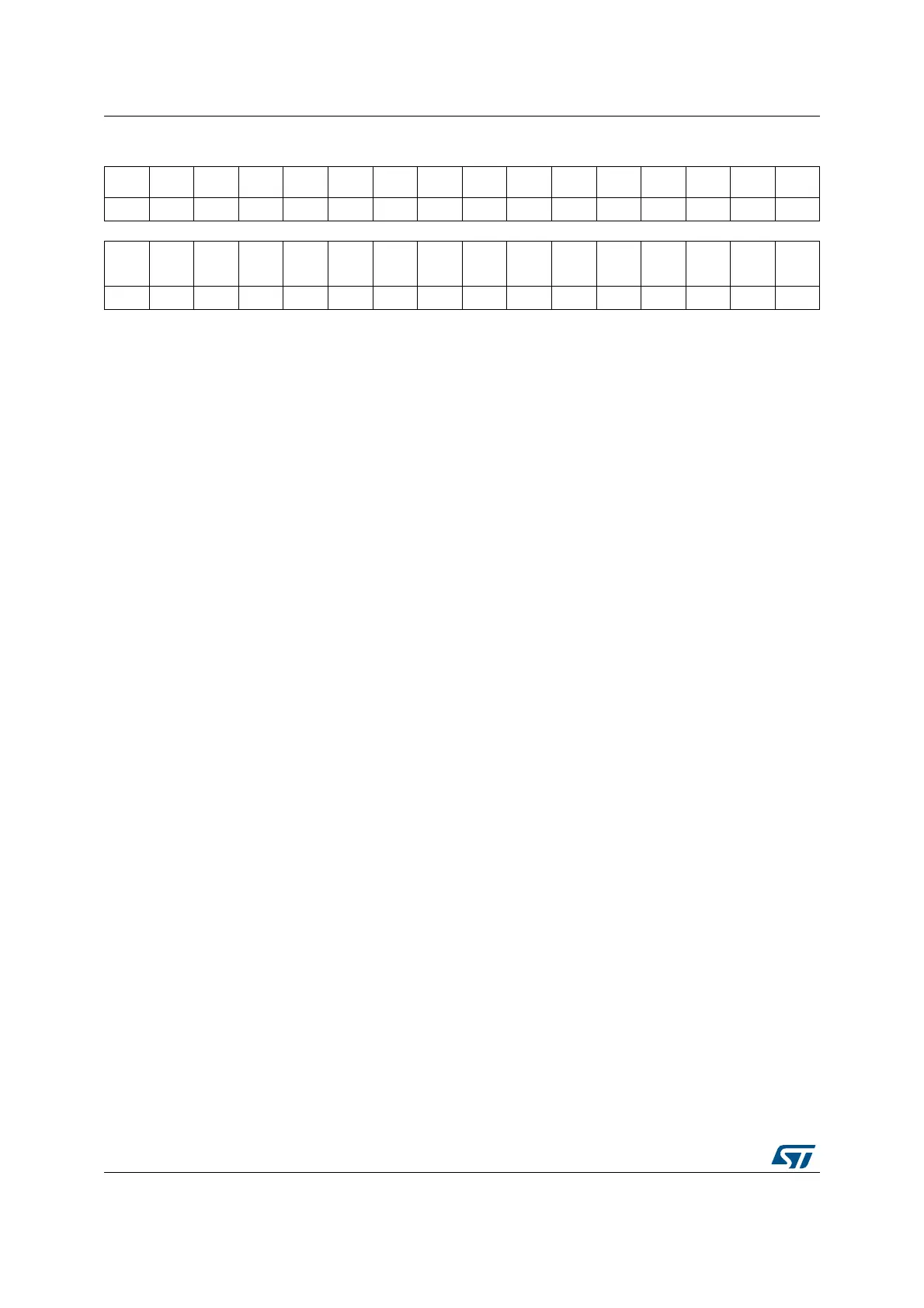

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. NAK Res.

PKTD

RPSTS

Res. Res.

TXFIF

OUD

RN

TXFE

IN

EPNE

IN

EPNM

ITTXFE TOC

AHB

ERR

EP

DISD

XFRC

rc_w1 rc_w1 rc_w1 r r rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1

Bits 31:14 Reserved, must be kept at reset value.

Bit 13 NAK: NAK input

The core generates this interrupt when a NAK is transmitted or received by the device. In

case of isochronous IN endpoints the interrupt gets generated when a zero length packet is

transmitted due to unavailability of data in the Tx FIFO.

Bit 12 Reserved, must be kept at reset value.

Bit 11 PKTDRPSTS: Packet dropped status

This bit indicates to the application that an ISOC OUT packet has been dropped. This bit

does not have an associated mask bit and does not generate an interrupt.

Bit 10 Reserved, must be kept at reset value.

Bit 9 Reserved, must be kept at reset value.

Bit 8 TXFIFOUDRN: Transmit Fifo Underrun (TxfifoUndrn)

The core generates this interrupt when it detects a transmit FIFO underrun condition for this

endpoint. Dependency: This interrupt is valid only when Thresholding is enabled

Bit 7 TXFE: Transmit FIFO empty

This interrupt is asserted when the Tx FIFO for this endpoint is either half or completely

empty. The half or completely empty status is determined by the Tx FIFO Empty Level bit in

the OTG_GAHBCFG register (TXFELVL bit in OTG_GAHBCFG).

Bit 6 INEPNE: IN endpoint NAK effective

This bit can be cleared when the application clears the IN endpoint NAK by writing to the

CNAK bit in OTG_DIEPCTLx.

This interrupt indicates that the core has sampled the NAK bit set (either by the application

or by the core). The interrupt indicates that the IN endpoint NAK bit set by the application

has taken effect in the core.

This interrupt does not guarantee that a NAK handshake is sent on the USB. A STALL bit

takes priority over a NAK bit.

Bit 5 INEPNM: IN token received with EP mismatch

Indicates that the data in the top of the non-periodic TxFIFO belongs to an endpoint other

than the one for which the IN token was received. This interrupt is asserted on the endpoint

for which the IN token was received.

Bit 4 ITTXFE: IN token received when Tx FIFO is empty

Indicates that an IN token was received when the associated Tx FIFO (periodic/non-

periodic) was empty. This interrupt is asserted on the endpoint for which the IN token was

received.

Loading...

Loading...