Reset and clock control (RCC) RM0390

168/1328 RM0390 Rev 4

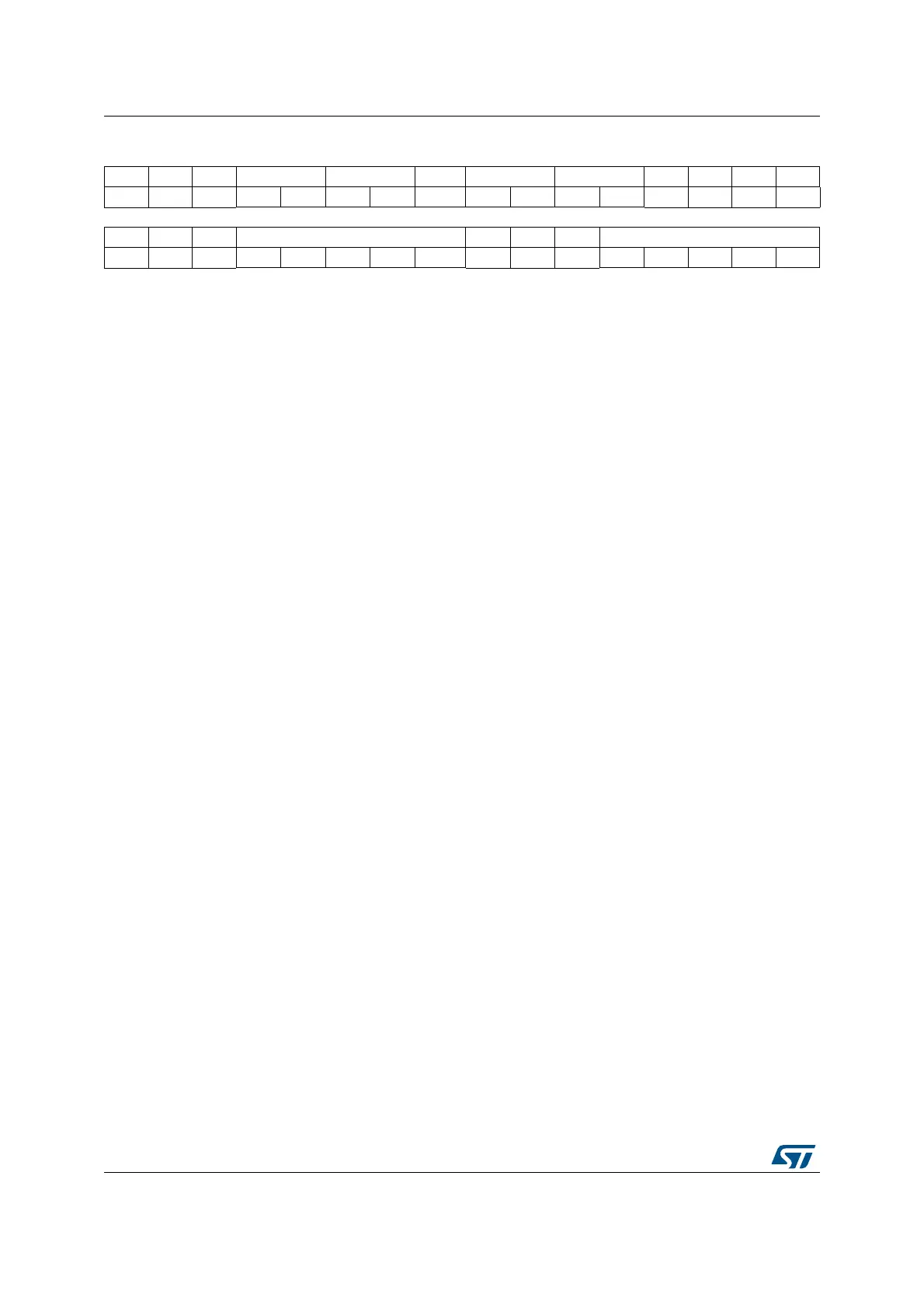

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. I2S2SRC I2S1SRC TIMPRE SAI2SRC SAI1SRC Res. Res. Res. Res.

rw rw rw rw rw rw rw rw rw

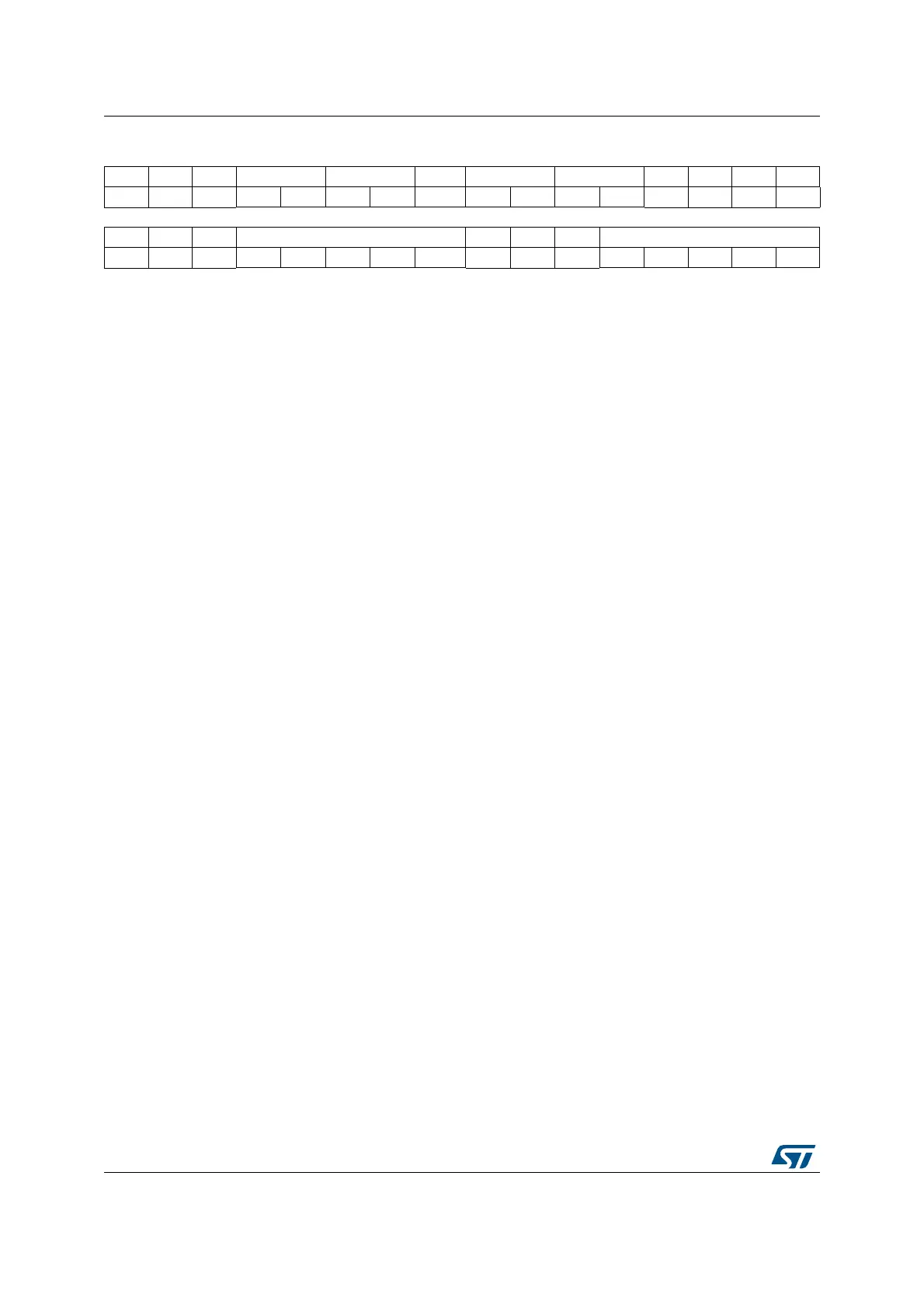

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. PLLSAIDIVQ Res. Res. Res. PLLIS2DIVQ

rw rw rw rw rw rw rw rw rw rw

Bits 31:29 Reserved, must be kept at reset value.

Bits 28:27 I2S2SRC: I2S APB2 clock source selection

Set and reset by software to control the frequency of the APB2 I2S clock.

These bits should be written when the PLL, PLLSAI and PLLI2S are disabled.

00: I2S2 clock frequency = f

(PLLI2S_R)

01: I2S2 clock frequency = I2S_CKIN Alternate function input frequency

10: I2S2 clock frequency = f

(PLL_R)

11: I2S2 clock frequency = HSI/HSE depends on PLLSRC bit (PLLCFGR[22])

Bits 26:25 I2S1SRC: I2S APB1 clock source selection

Set and reset by software to control the frequency of the APB1 I2S clock.

These bits should be written when the PLL, PLLSAI and PLLI2S are disabled.

00: I2S1 clock frequency = f

(PLLI2S_R)

01: I2S1 clock frequency = I2S_CKIN Alternate function input frequency

10: I2S1 clock frequency = f

(PLL_R)

11: I2S1 clock frequency = HSI/HSE depends on PLLSRC bit (PLLCFGR[22])

Bit 24 TIMPRE: Timers clocks prescalers selection

This bit is set and reset by software to control the clock frequency of all the timers connected

to APB1 and APB2 domain.

0: If the APB prescaler (PPRE1, PPRE2 in the RCC_CFGR register) is configured to a

division factor of 1, TIMxCLK = PCLKx. Otherwise, the timer clock frequencies are set to

twice to the frequency of the APB domain to which the timers are connected:

TIMxCLK = 2xPCLKx.

1:If the APB prescaler (PPRE1, PPRE2 in the RCC_CFGR register) is configured to a

division factor of 1, 2 or 4, TIMxCLK = HCLK. Otherwise, the timer clock frequencies are set

to four times to the frequency of the APB domain to which the timers are connected:

TIMxCLK = 4xPCLKx.

Bits 23:22 SAI2SRC: SAI2 clock source selection

These bits are set and cleared by software to control the SAI2 clock frequency.

They should be written when the PLL, PLLSAI and PLLI2S are disabled.

00: SAI2 clock frequency = f

(PLLSAI_Q)

/ PLLSAIDIVQ

01: SAI2 clock frequency = f

(PLLI2S_Q)

/ PLLI2SDIVQ

10: SAI2 clock frequency = f

(PLL_R)

11: SAI2 clock frequency = HSI/HSE depends on PLLSRC (PLLCFGR[22])

Bits 21:20 SAI1SRC: SAI1 clock source selection

These bits are set and cleared by software to control the SAI1 clock frequency.

They should be written when the PLLSAI and PLLI2S are disabled.

00: SAI1 clock frequency = f

(PLLSAI_Q)

/ PLLSAIDIVQ

01: SAI1 clock frequency = f

(PLLI2S_Q)

/ PLLI2SDIVQ

10: SAI1 clock frequency = f

(PLL_R)

11: I2S_CKIN Alternate function input frequency

Bits 19:13 Reserved, must be kept at reset value.

Loading...

Loading...