Flexible memory controller (FMC) RM0390

290/1328 RM0390 Rev 4

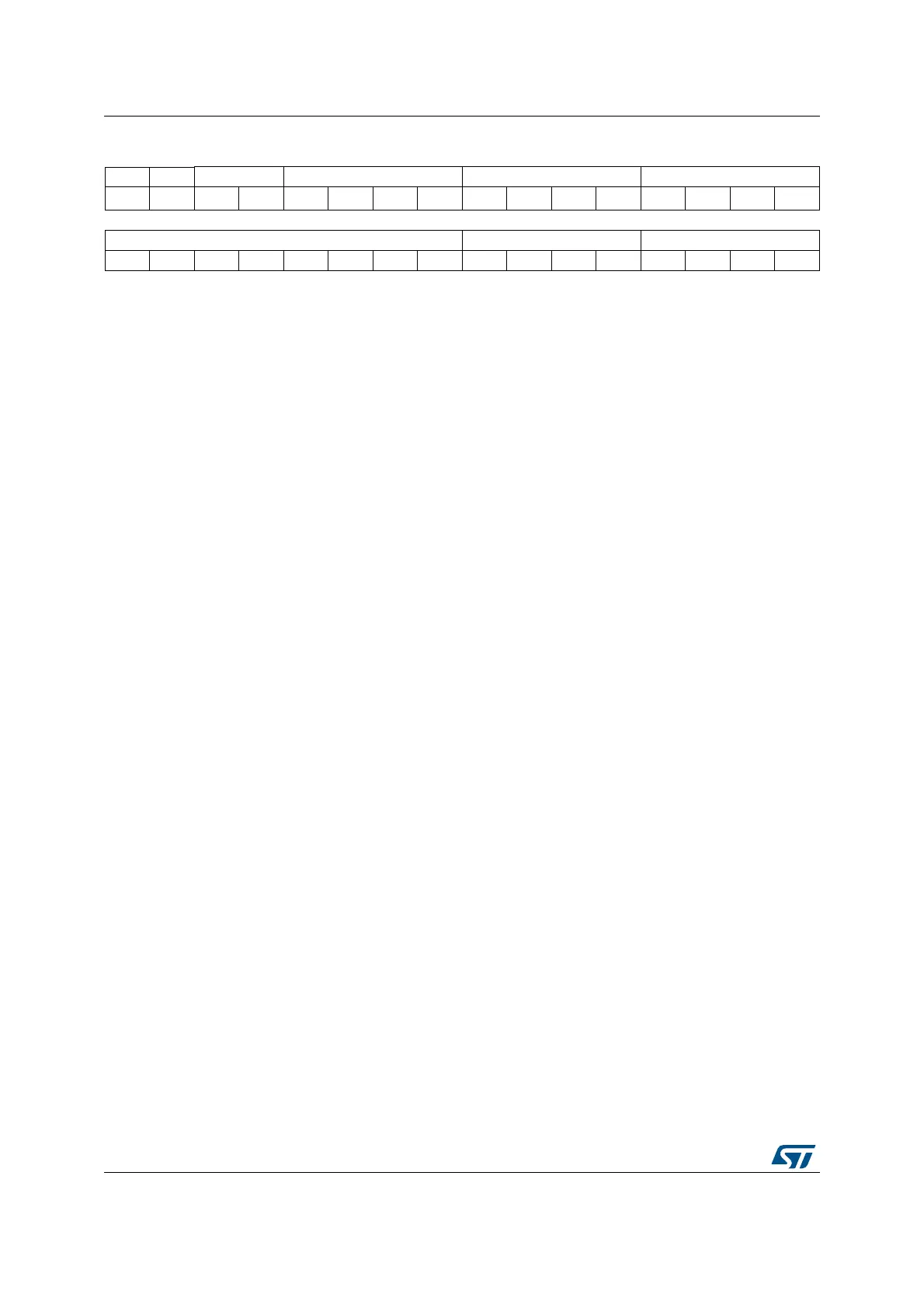

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. ACCMOD DATLAT CLKDIV BUSTURN

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

DATAST ADDHLD ADDSET

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:30 Reserved, must be kept at reset value

Bits 29:28 ACCMOD[1:0]: Access mode

Specifies the asynchronous access modes as shown in the timing diagrams. These bits are

taken into account only when the EXTMOD bit in the FMC_BCRx register is 1.

00: access mode A

01: access mode B

10: access mode C

11: access mode D

Bits 27:24 DATLAT[3:0]: (see note below bit descriptions): Data latency for synchronous memory

For synchronous access with read/write burst mode enabled (BURSTEN / CBURSTRW bits

set), defines the number of memory clock cycles (+2) to issue to the memory before

reading/writing the first data:

This timing parameter is not expressed in HCLK periods, but in FMC_CLK periods.

For asynchronous access, this value is don't care.

0000: Data latency of 2 CLK clock cycles for first burst access

1111: Data latency of 17 CLK clock cycles for first burst access (default value after reset)

Bits 23:20 CLKDIV[3:0]: Clock divide ratio (for FMC_CLK signal)

Defines the period of FMC_CLK clock output signal, expressed in number of HCLK cycles:

0000: Reserved

0001: FMC_CLK period = 2 × HCLK periods

0010: FMC_CLK period = 3 × HCLK periods

1111: FMC_CLK period = 16 × HCLK periods (default value after reset)

In asynchronous NOR Flash, SRAM or PSRAM accesses, this value is don’t care.

Note: Refer to Section 11.5.5: Synchronous transactions for FMC_CLK divider ratio formula)

Loading...

Loading...