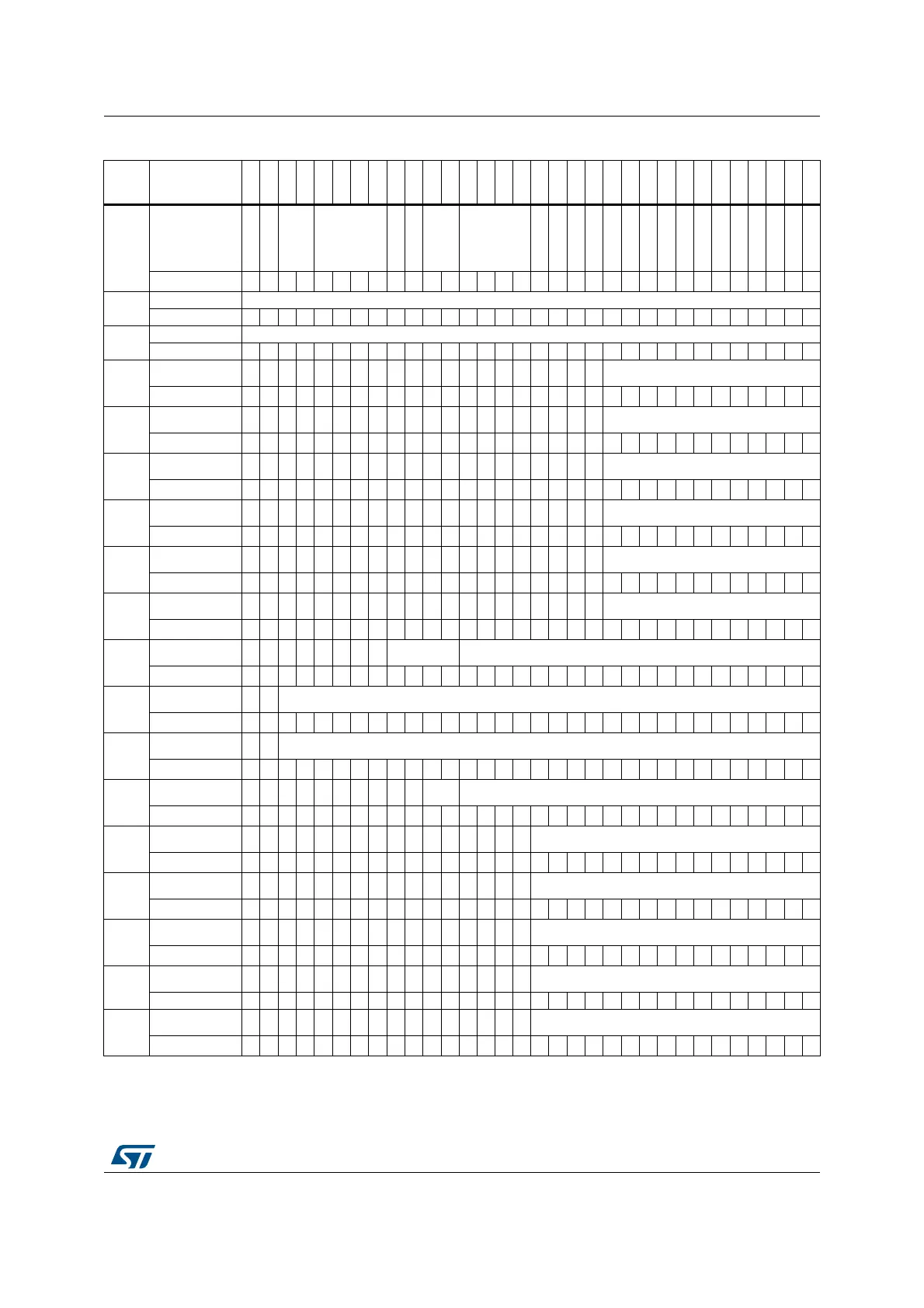

RM0390 Rev 4 399/1328

RM0390 Analog-to-digital converter (ADC)

400

0x08

ADC_CR2

Res.

SWSTART

EXTEN[1:0]

EXTSEL [3:0]

Res.

JSWSTART

JEXTEN[1:0]

JEXTSEL

[3:0]

Res.

Res.

Res.

Res.

ALIGN

EOCS

DDS

DMA

Res.

Res.

Res.

Res.

Res.

Res.

CONT

ADON

Reset value 0000000 0000000 00 0 00

0x0C

ADC_SMPR1 Sample time bits SMPx_x

Reset value 00000000000000000000000000000000

0x10

ADC_SMPR2 Sample time bits SMPx_x

Reset value 00000000000000000000000000000000

0x14

ADC_JOFR1

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

JOFFSET1[11:0]

Reset value 000000000000

0x18

ADC_JOFR2

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

JOFFSET2[11:0]

Reset value 000000000000

0x1C

ADC_JOFR3

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

JOFFSET3[11:0]

Reset value 000000000000

0x20

ADC_JOFR4

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

JOFFSET4[11:0]

Reset value 000000000000

0x24

ADC_HTR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

HT[11:0]

Reset value 111111111111

0x28

ADC_LTR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

LT[11:0]

Reset value 000000000000

0x2C

ADC_SQR1

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

L[3:0] Regular channel sequence SQx_x bits

Reset value 000000000000000000000000

0x30

ADC_SQR2

Res.

Res.

Regular channel sequence SQx_x bits

Reset value 000000000000000000000000000000

0x34

ADC_SQR3

Res.

Res.

Regular channel sequence SQx_x bits

Reset value 000000000000000000000000000000

0x38

ADC_JSQR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

JL[1:0] Injected channel sequence JSQx_x bits

Reset value 0000000000000000000000

0x3C

ADC_JDR1

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

JDATA[15:0]

Reset value 0000000000000000

0x40

ADC_JDR2

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

JDATA[15:0]

Reset value 0000000000000000

0x44

ADC_JDR3

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

JDATA[15:0]

Reset value 0000000000000000

0x48

ADC_JDR4

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

JDATA[15:0]

Reset value 0000000000000000

0x4C

ADC_DR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Regular DATA[15:0]

Reset value 0000000000000000

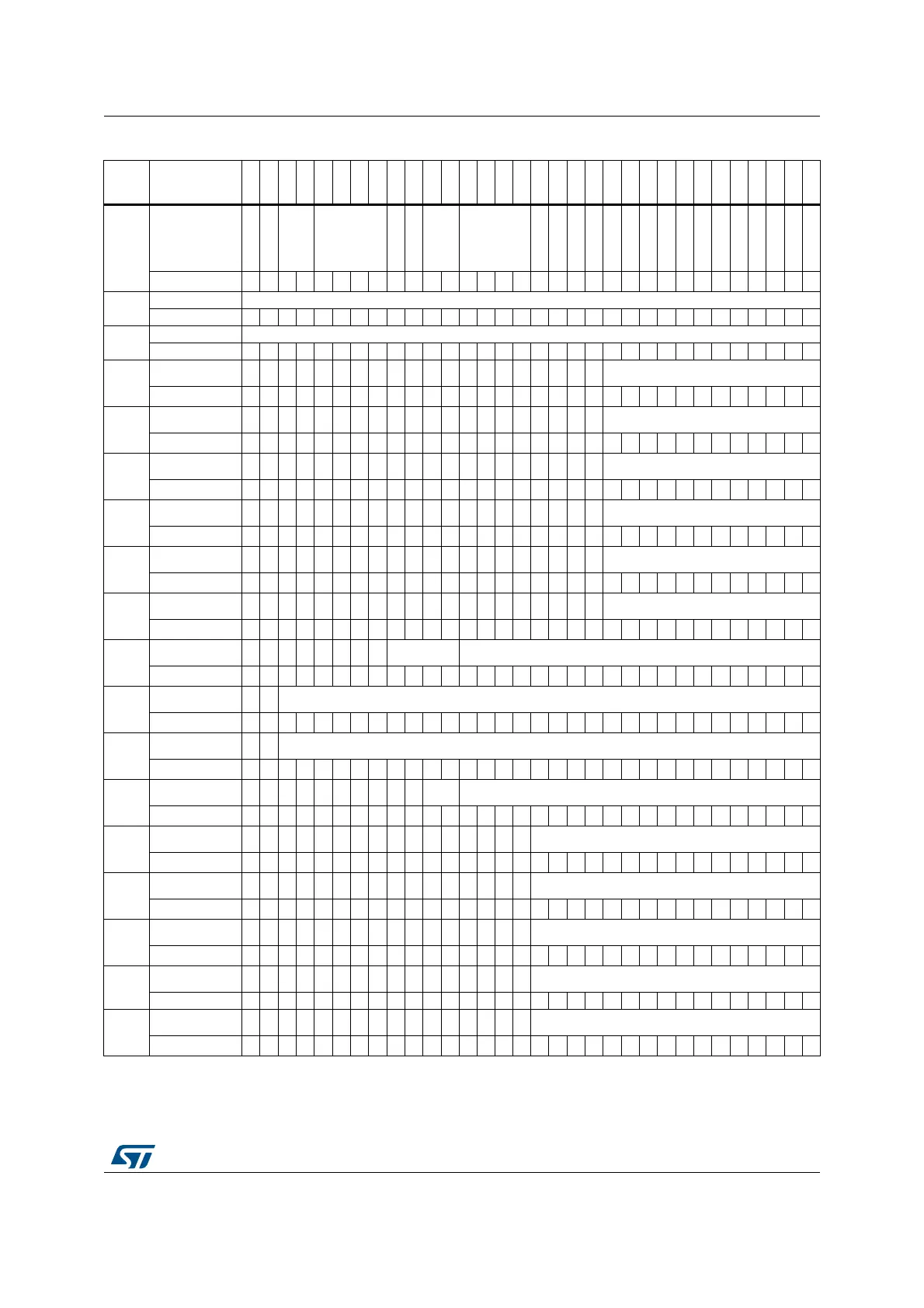

Table 91. ADC register map and reset values for each ADC (continued)

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Loading...

Loading...