Digital camera interface (DCMI) RM0390

436/1328 RM0390 Rev 4

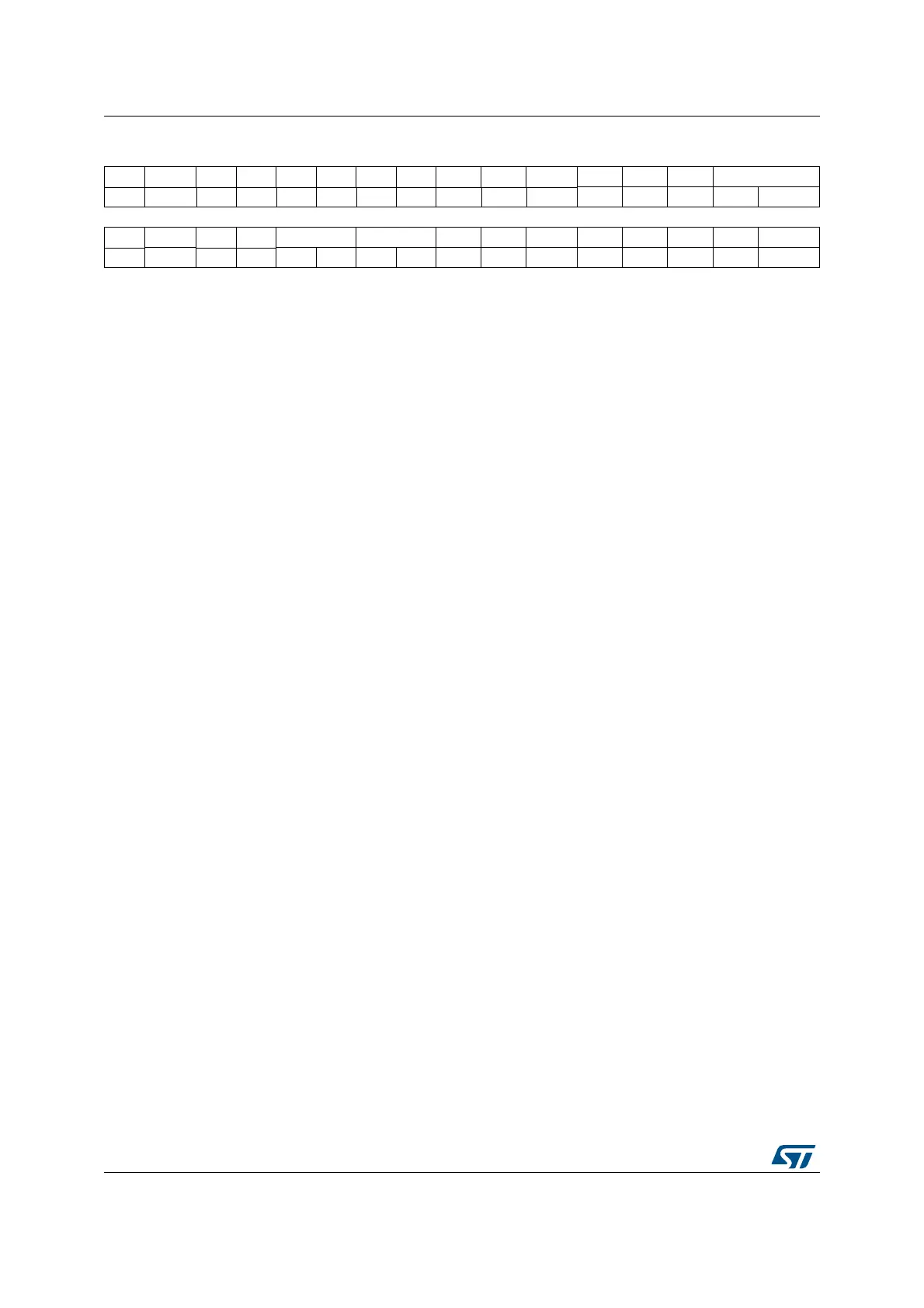

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. OELS LSM OEBS BSM[1:0]

rw rw rw rw rw

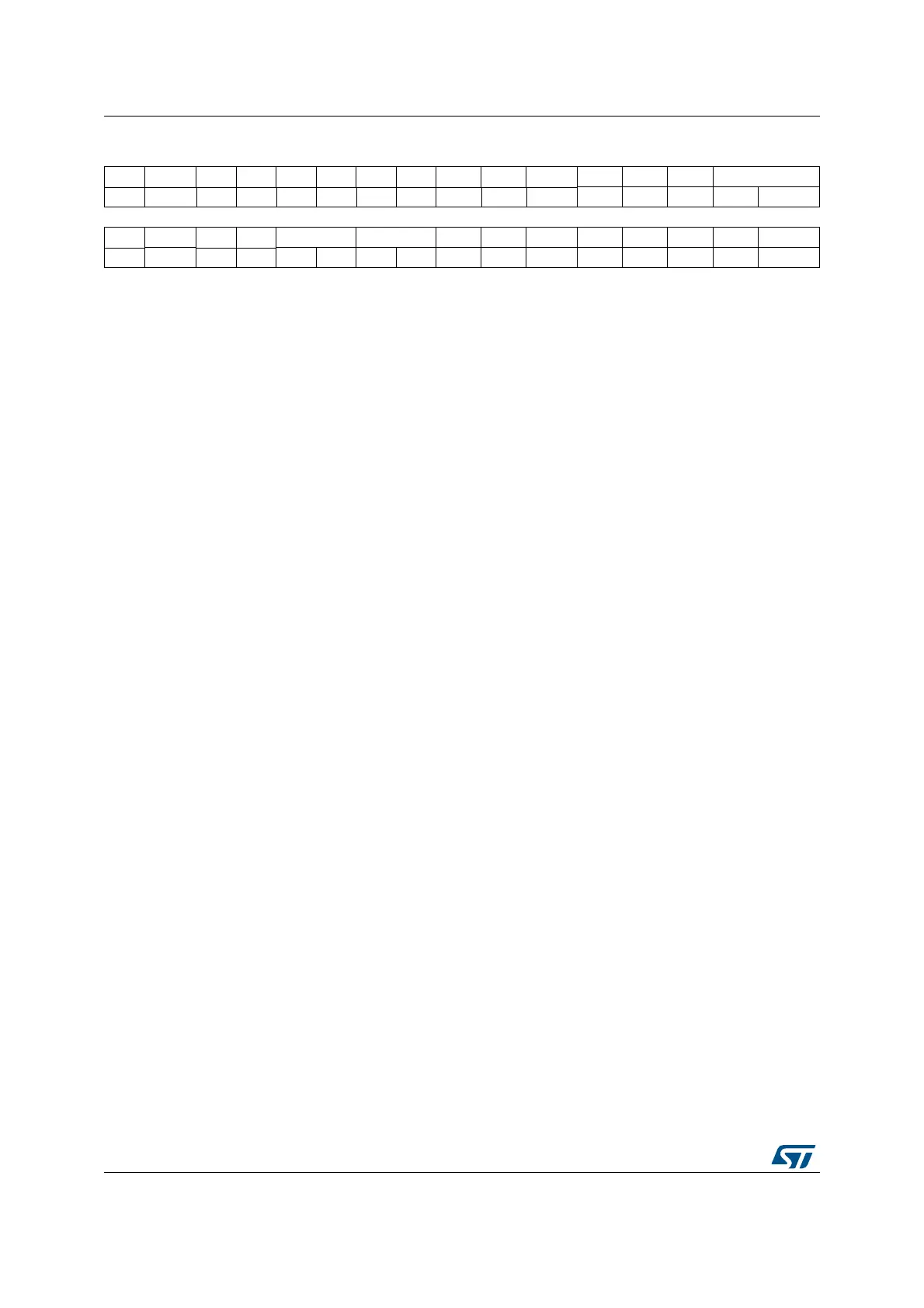

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. ENABLE Res. Res. EDM[1:0] FCRC[1:0] VSPOL HSPOL PCKPOL ESS JPEG CROP CM CAPTURE

rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:21 Reserved, must be kept at reset value.

Bit 20 OELS: Odd/Even Line Select (Line Select Start)

This bit works in conjunction with LSM field (LSM = 1)

0: Interface captures first line after the frame start, second one being dropped

1: Interface captures second line from the frame start, first one being dropped

Bit 19 LSM: Line Select mode

0: Interface captures all received lines

1: Interface captures one line out of two.

Bit 18 OEBS: Odd/Even Byte Select (Byte Select Start)

This bit works in conjunction with BSM field (BSM <> 00)

0: Interface captures first data (byte or double byte) from the frame/line start,

second one being dropped

1: Interface captures second data (byte or double byte) from the frame/line start,

first one being dropped

Bits 17:16 BSM[1:0]: Byte Select mode

00: Interface captures all received data

01: Interface captures every other byte from the received data

10: Interface captures one byte out of four

11: Interface captures two bytes out of four

Note: This mode only work for EDM[1:0]=00. For all other EDM values, this bit

field must be programmed to the reset value.

Bit 15 Reserved, must be kept at reset value.

Bit 14 ENABLE: DCMI enable

0: DCMI disabled

1: DCMI enabled

Note: The DCMI configuration registers should be programmed correctly before

enabling this Bit

Bits 13:12 Reserved, must be kept at reset value.

Bits 11:10 EDM[1:0]: Extended data mode

00: Interface captures 8-bit data on every pixel clock

01: Interface captures 10-bit data on every pixel clock

10: Interface captures 12-bit data on every pixel clock

11: Interface captures 14-bit data on every pixel clock

Bits 9:8 FCRC[1:0]: Frame capture rate control

These bits define the frequency of frame capture. They are meaningful only in

Continuous grab mode. They are ignored in snapshot mode.

00: All frames are captured

01: Every alternate frame captured (50% bandwidth reduction)

10: One frame in 4 frames captured (75% bandwidth reduction)

11: reserved

Loading...

Loading...