Real-time clock (RTC) RM0390

678/1328 RM0390 Rev 4

Note: This register can be written in initialization mode only (RTC_ISR/INITF = ‘1’).

This register is write protected. The write access procedure is described in RTC register

write protection.

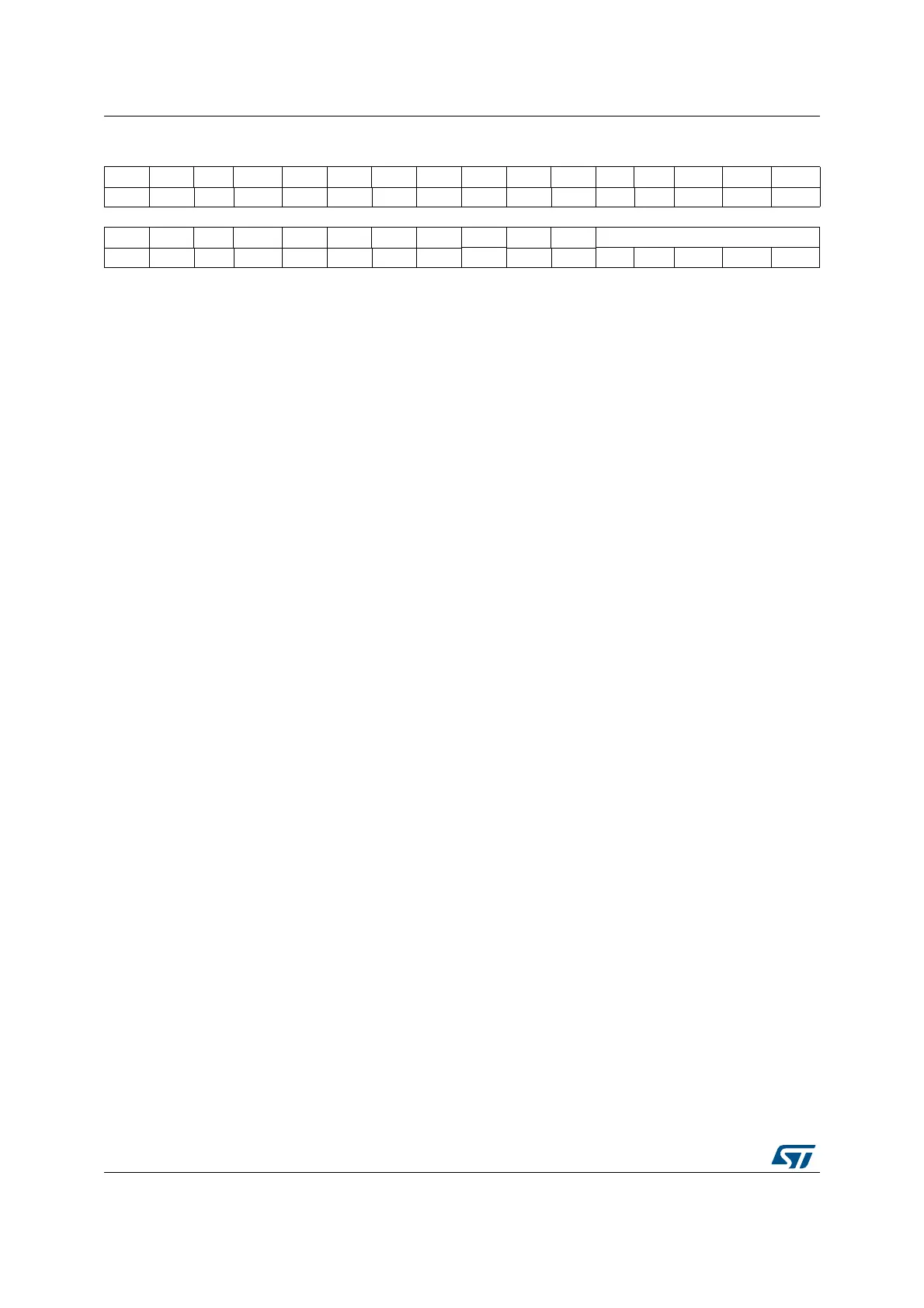

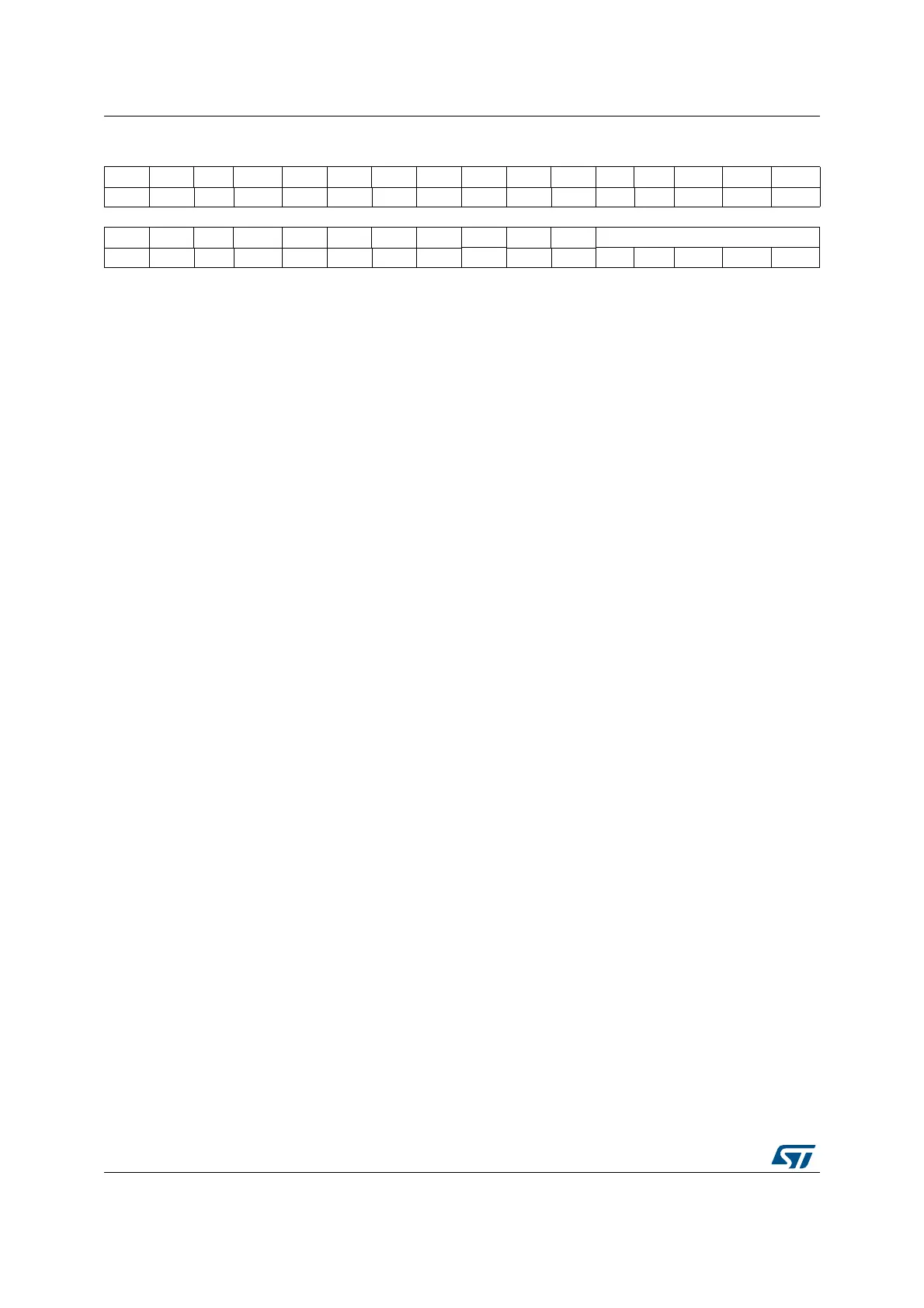

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15141312111098765432 1 0

Res. Res. Res. Res. Res. Res. Res. Res. DCS Res. Res. DC[4:0]

rw rw rw rw rw rw

Bits 31:8 Reserved, must be kept at reset value

Bit 7 DCS: Digital calibration sign

0: Positive calibration: calendar update frequency is increased

1: Negative calibration: calendar update frequency is decreased

Bits 6:5 Reserved, must be kept at reset value.

Bits 4:0 DC[4:0]: Digital calibration

DCS = 0 (positive calibration)

00000: +0 ppm

00001: +4 ppm (rounded value)

00010: +8 ppm (rounded value)

..

11111: +126 ppm (rounded value)

DCS = 1 (negative calibration)

00000: -0 ppm

00001: -2 ppm (rounded value)

00010: -4 ppm (rounded value)

..

11111: - 63 ppm (rounded value)

Refer to Case of RTCCLK=32.768 kHz and PREDIV_A+1=128 for the exact step value.

Loading...

Loading...