Universal synchronous asynchronous receiver transmitter (USART) RM0390

812/1328 RM0390 Rev 4

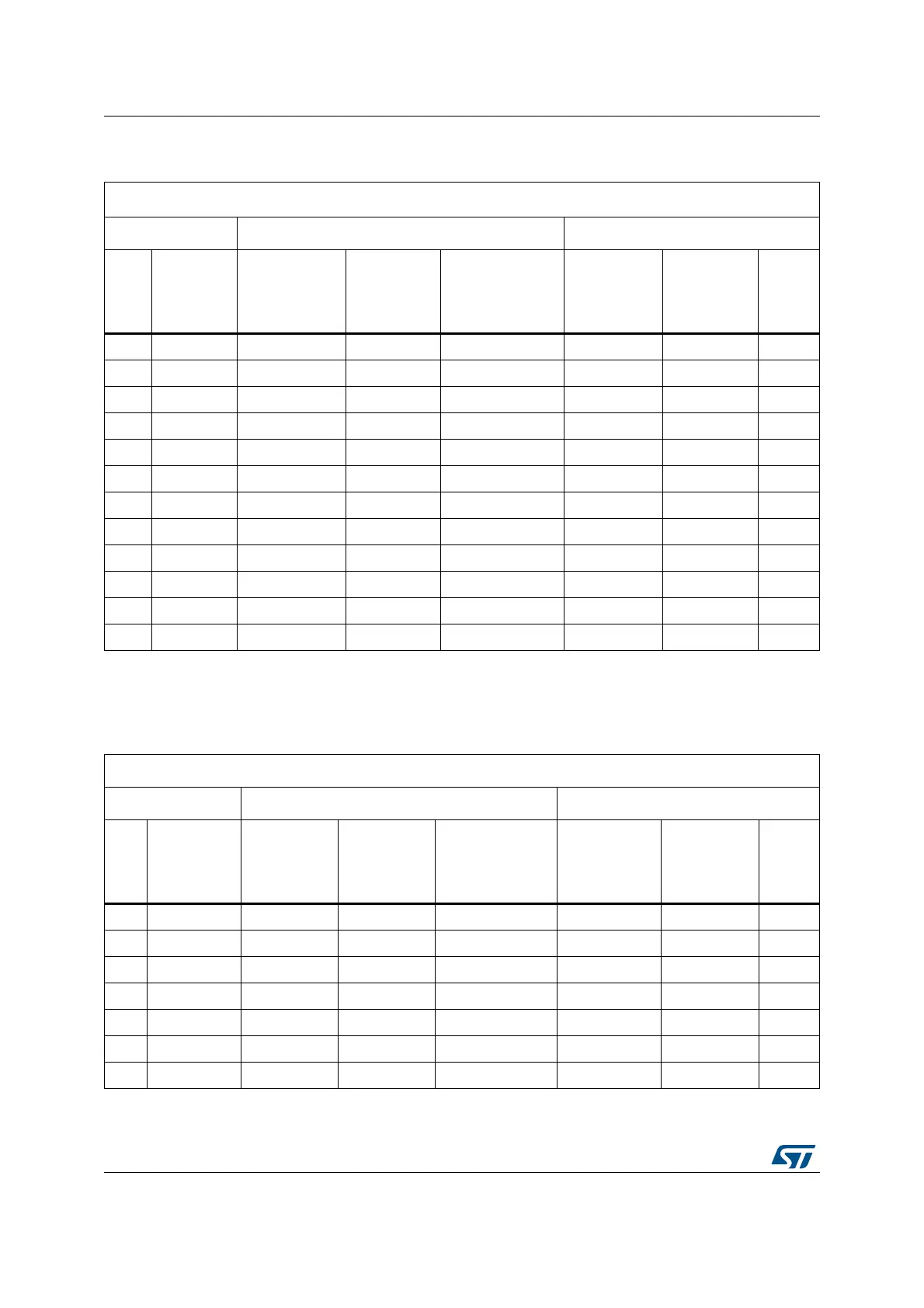

Table 150. Error calculation for programmed baud rates at f

PCLK

= 16 MHz or f

PCLK

= 24 MHz,

oversampling by 8

(1)

Oversampling by 8 (OVER8=1)

Baud rate f

PCLK

= 16 MHz f

PCLK

= 24 MHz

S.No Desired Actual

Value

programmed

in the baud

rate register

% Error =

(Calculated -

Desired) B.rate /

Desired B.rate

Actual

Value

programmed

in the baud

rate register

% Error

1 1.2 KBps 1.2 KBps 1666.625 0 1.2 KBps 2500 0

2 2.4 KBps 2.4 KBps 833.375 0 2.4 KBps 1250 0

3 9.6 KBps 9.598 KBps 208.375 0.02 9.6 KBps 312.5 0

4 19.2 KBps 19.208 KBps 104.125 0.04 19.2 KBps 156.25 0

5 38.4 KBps 38.369 KBps 52.125 0.08 38.4 KBps 78.125 0

6 57.6 KBps 57.554 KBps 34.75 0.08 57.554 KBps 52.125 0.08

7 115.2 KBps 115.108 KBps 17.375 0.08 115.385 KBps 26 0.16

8 230.4 KBps 231.884 KBps 8.625 0.64 230.769 KBps 13 0.16

9 460.8 KBps 457.143 KBps 4.375 0.79 461.538 KBps 6.5 0.16

10 921.6 KBps 941.176 KBps 2.125 2.12 923.077 KBps 3.25 0.16

11 2 MBps 2000 KBps 1 0 2000 KBps 1.5 0

12 3 MBps NA NA NA 3000 KBps 1 0

1. The lower the CPU clock the lower the accuracy for a particular baud rate. The upper limit of the achievable baud rate can

be fixed with these data.

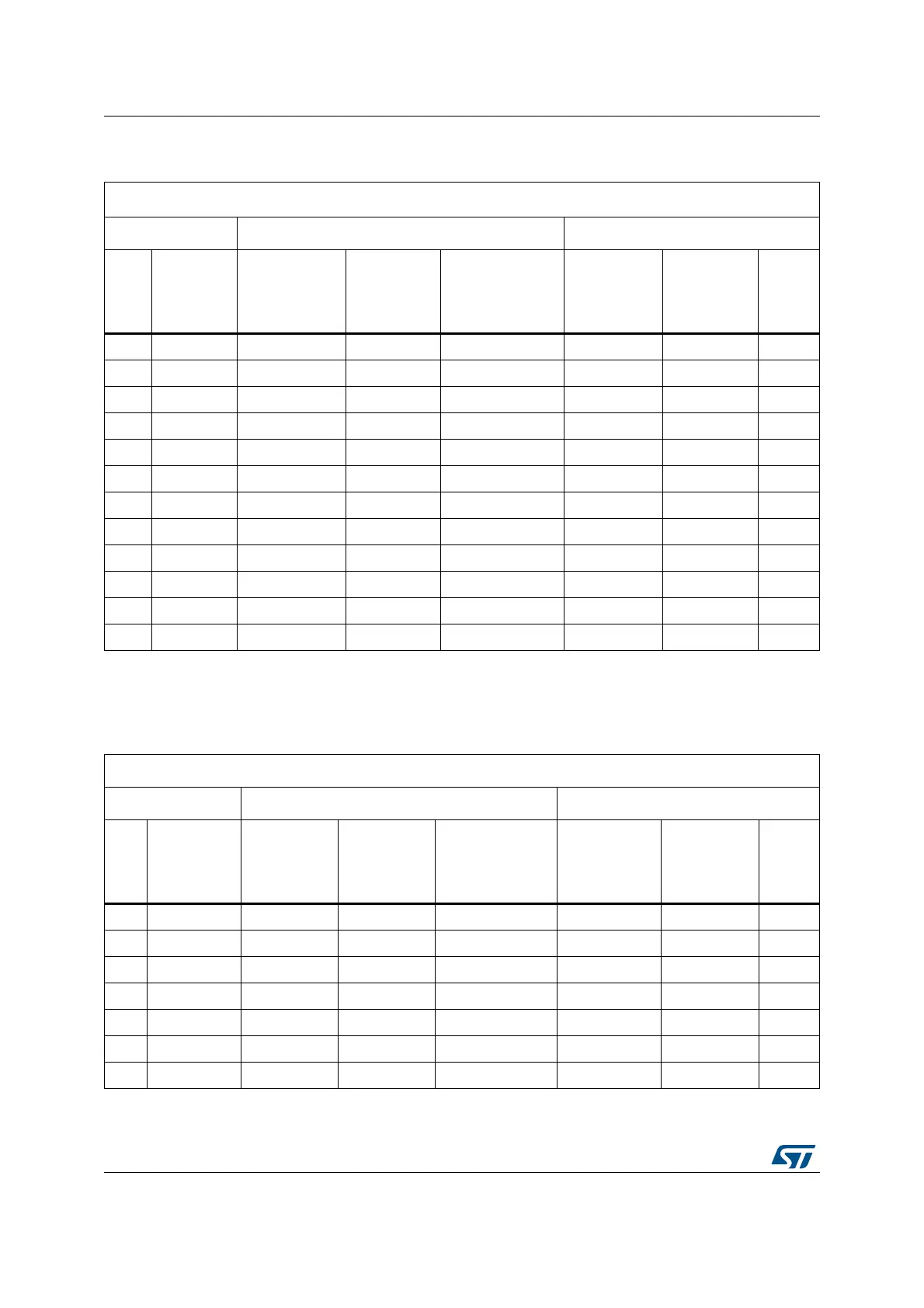

Table 151. Error calculation for programmed baud rates at f

PCLK

= 8 MHz or f

PCLK

= 16 MHz,

oversampling by 16

(1)

Oversampling by 16 (OVER8=0)

Baud rate f

PCLK

= 8 MHz f

PCLK

= 16 MHz

S.No Desired Actual

Value

programmed

in the baud

rate register

% Error =

(Calculated -

Desired)B.Rate

/Desired B.Rate

Actual

Value

programmed

in the baud

rate register

% Error

1 2.4 KBps 2.400 KBps 208.3125 0.00% 2.400 KBps 416.6875 0.00%

2 9.6 KBps 9.604 KBps 52.0625 0.04% 9.598 KBps 104.1875 0.02%

3 19.2 KBps 19.185 KBps 26.0625 0.08% 19.208 KBps 52.0625 0.04%

4 57.6 KBps 57.554 KBps 8.6875 0.08% 57.554 KBps 17.3750 0.08%

5 115.2 KBps 115.942 KBps 4.3125 0.64% 115.108 KBps 8.6875 0.08%

6 230.4 KBps 228.571 KBps 2.1875 0.79% 231.884 KBps 4.3125 0.64%

7 460.8 KBps 470.588 KBps 1.0625 2.12% 457.143 KBps 2.1875 0.79%

Loading...

Loading...