Controller area network (bxCAN) RM0390

1058/1328 RM0390 Rev 4

CAN receive FIFO 1 register (CAN_RF1R)

Address offset: 0x10

Reset value: 0x0000 0000

Bits 31:6 Reserved, must be kept at reset value.

Bit 5 RFOM0

: Release FIFO 0 output mailbox

Set by software to release the output mailbox of the FIFO. The output mailbox can only be

released when at least one message is pending in the FIFO. Setting this bit when the FIFO

is empty has no effect. If at least two messages are pending in the FIFO, the software has to

release the output mailbox to access the next message.

Cleared by hardware when the output mailbox has been released.

Bit 4 FOVR0

: FIFO 0 overrun

This bit is set by hardware when a new message has been received and passed the filter

while the FIFO was full.

This bit is cleared by software.

Bit 3 FULL0

: FIFO 0 full

Set by hardware when three messages are stored in the FIFO.

This bit is cleared by software.

Bit 2 Reserved, must be kept at reset value.

Bits 1:0 FMP0[1:0]

: FIFO 0 message pending

These bits indicate how many messages are pending in the receive FIFO.

FMP is increased each time the hardware stores a new message in to the FIFO. FMP is

decreased each time the software releases the output mailbox by setting the RFOM0 bit.

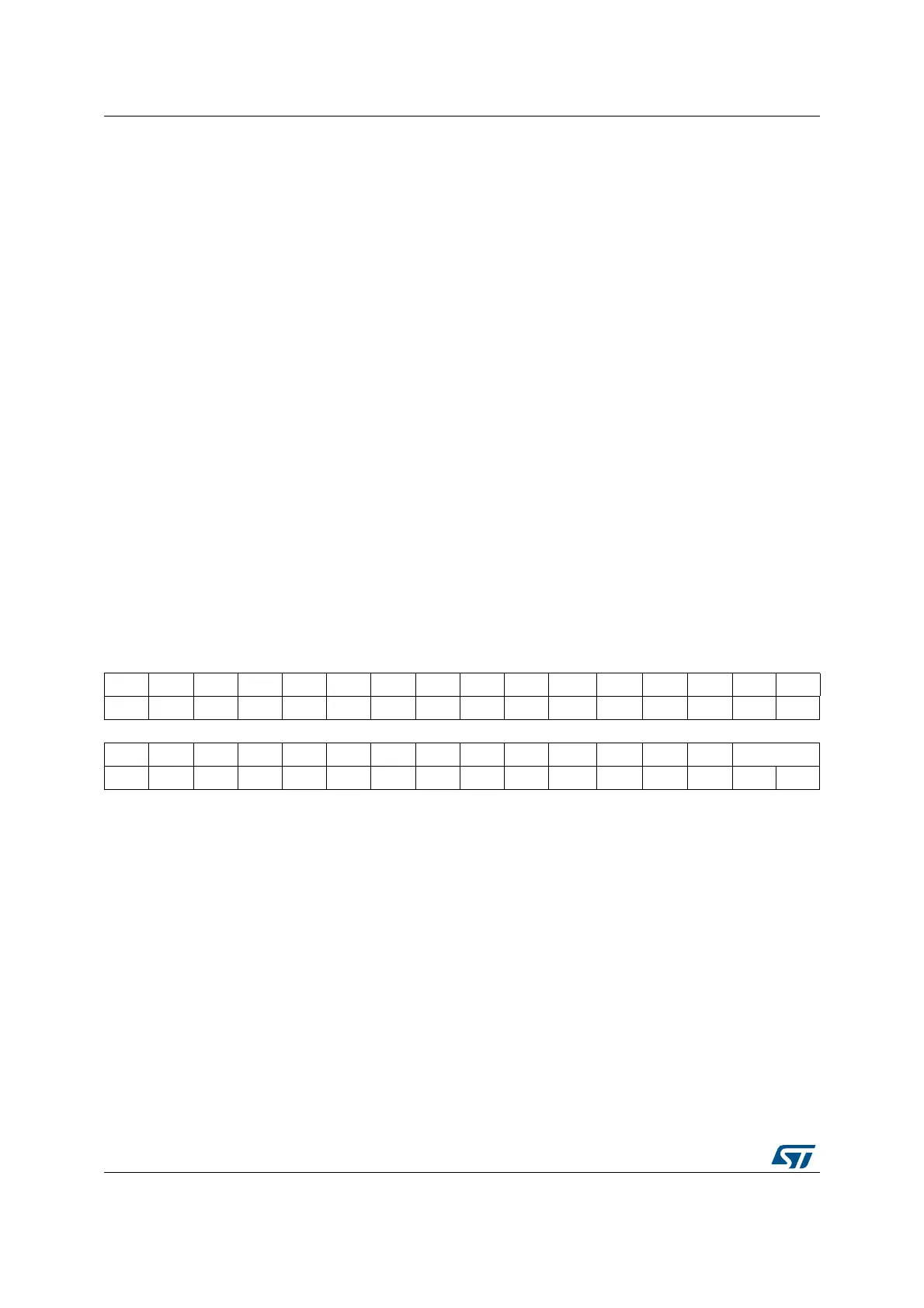

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

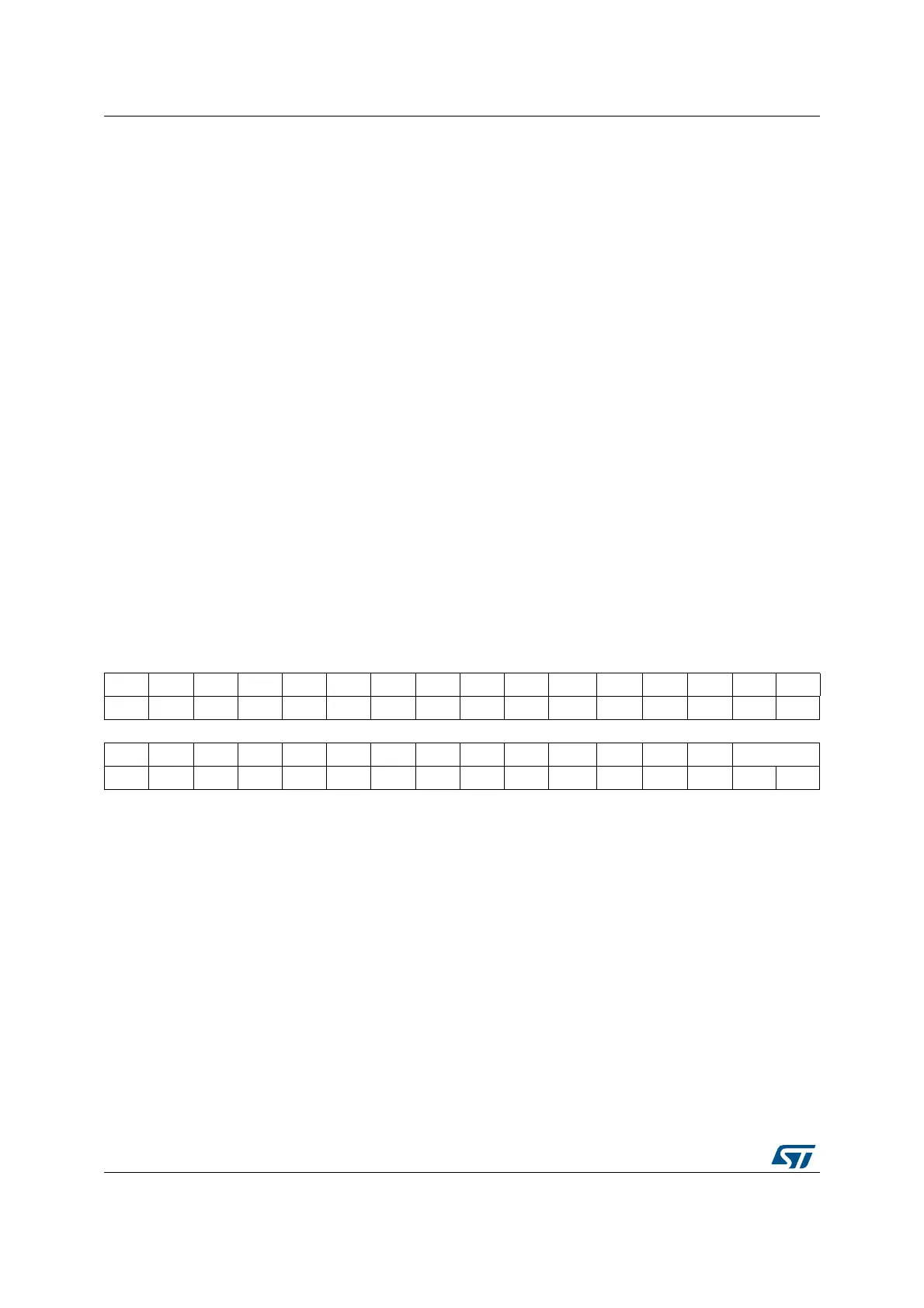

1514131211109876 5 4 3210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. RFOM1 FOVR1 FULL1 Res. FMP1[1:0]

rs rc_w1 rc_w1 r r

Bits 31:6 Reserved, must be kept at reset value.

Bit 5 RFOM1

: Release FIFO 1 output mailbox

Set by software to release the output mailbox of the FIFO. The output mailbox can only be

released when at least one message is pending in the FIFO. Setting this bit when the FIFO

is empty has no effect. If at least two messages are pending in the FIFO, the software has to

release the output mailbox to access the next message.

Cleared by hardware when the output mailbox has been released.

Bit 4 FOVR1

: FIFO 1 overrun

This bit is set by hardware when a new message has been received and passed the filter

while the FIFO was full.

This bit is cleared by software.

Loading...

Loading...