RM0390 Rev 4 1059/1328

RM0390 Controller area network (bxCAN)

1076

CAN interrupt enable register (CAN_IER)

Address offset: 0x14

Reset value: 0x0000 0000

Bit 3 FULL1: FIFO 1 full

Set by hardware when three messages are stored in the FIFO.

This bit is cleared by software.

Bit 2 Reserved, must be kept at reset value.

Bits 1:0 FMP1[1:0]

: FIFO 1 message pending

These bits indicate how many messages are pending in the receive FIFO1.

FMP1 is increased each time the hardware stores a new message in to the FIFO1. FMP is

decreased each time the software releases the output mailbox by setting the RFOM1 bit.

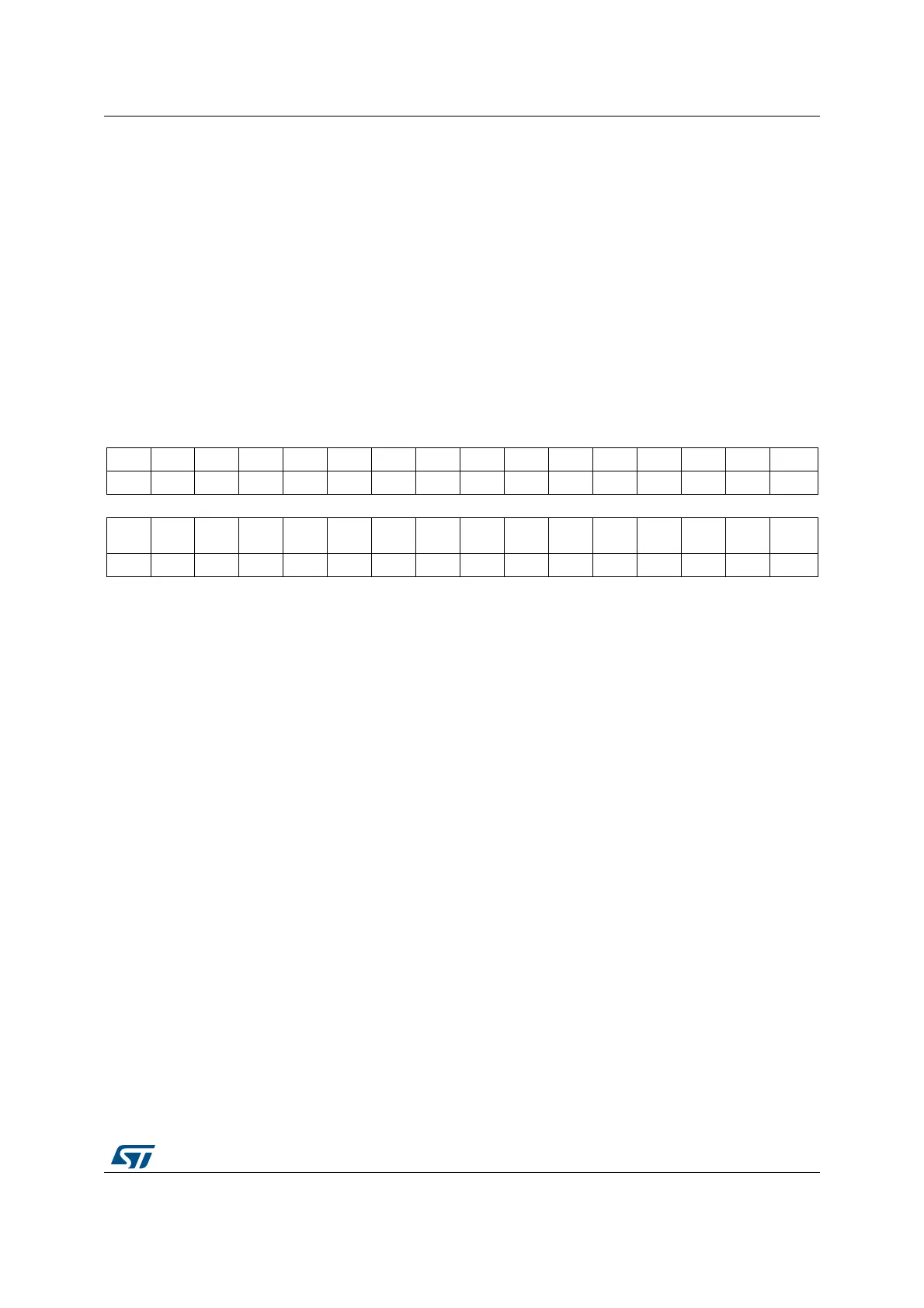

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. SLKIE WKUIE

rw rw

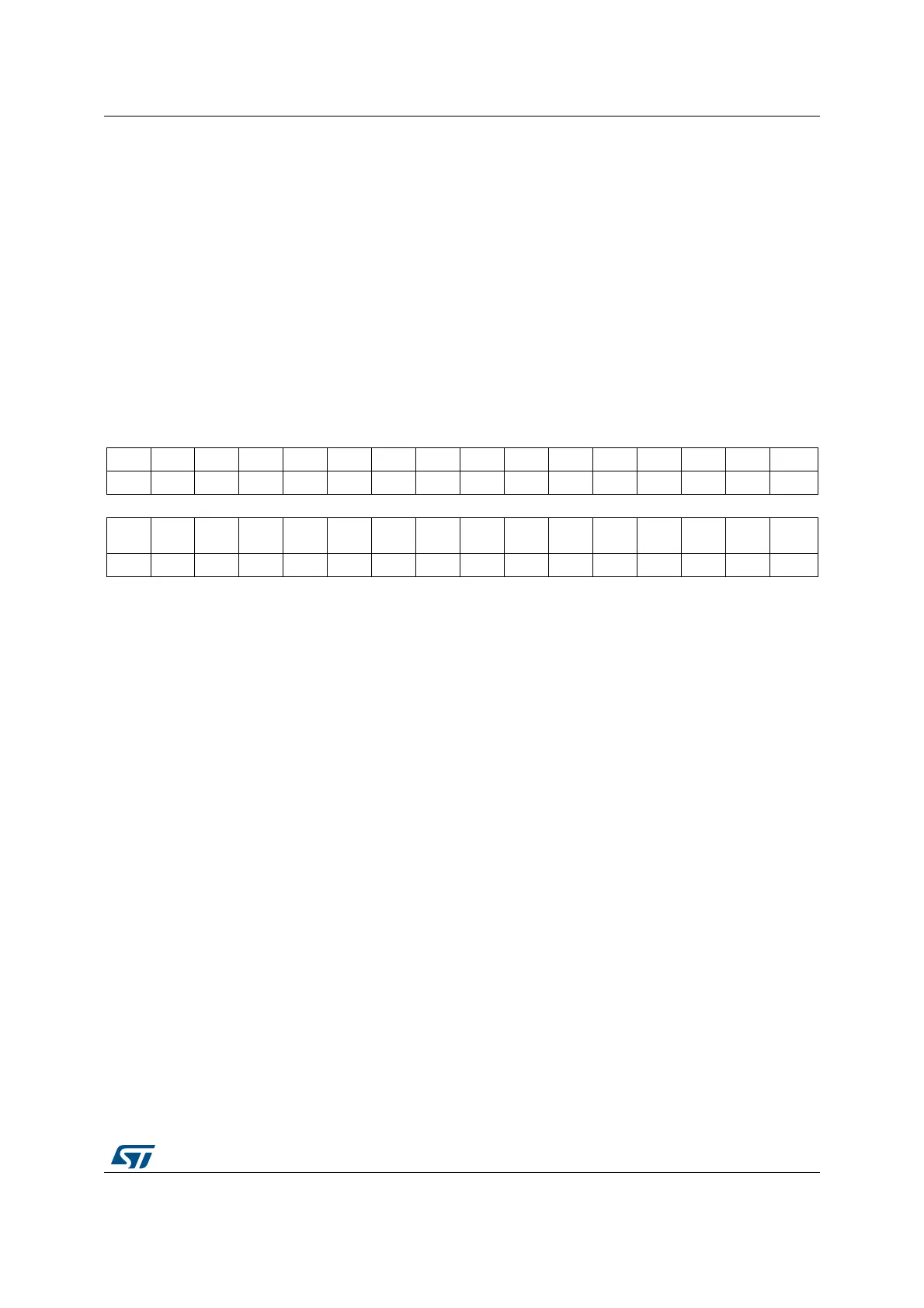

151413121110987654321 0

ERRIE Res. Res. Res.

LEC

IE

BOF

IE

EPV

IE

EWG

IE

Res.

FOV

IE1

FF

IE1

FMP

IE1

FOV

IE0

FF

IE0

FMP

IE0

TME

IE

rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:18 Reserved, must be kept at reset value.

Bit 17 SLKIE

: Sleep interrupt enable

0: No interrupt when SLAKI bit is set.

1: Interrupt generated when SLAKI bit is set.

Bit 16 WKUIE

: Wakeup interrupt enable

0: No interrupt when WKUI is set.

1: Interrupt generated when WKUI bit is set.

Bit 15 ERRIE

: Error interrupt enable

0: No interrupt will be generated when an error condition is pending in the CAN_ESR.

1: An interrupt will be generation when an error condition is pending in the CAN_ESR.

Bits 14:12 Reserved, must be kept at reset value.

Bit 11 LECIE

: Last error code interrupt enable

0: ERRI bit will not be set when the error code in LEC[2:0] is set by hardware on error

detection.

1: ERRI bit will be set when the error code in LEC[2:0] is set by hardware on error detection.

Bit 10 BOFIE

: Bus-off interrupt enable

0: ERRI bit will not be set when BOFF is set.

1: ERRI bit will be set when BOFF is set.

Bit 9 EPVIE

: Error passive interrupt enable

0: ERRI bit will not be set when EPVF is set.

1: ERRI bit will be set when EPVF is set.

Loading...

Loading...