Controller area network (bxCAN) RM0390

1060/1328 RM0390 Rev 4

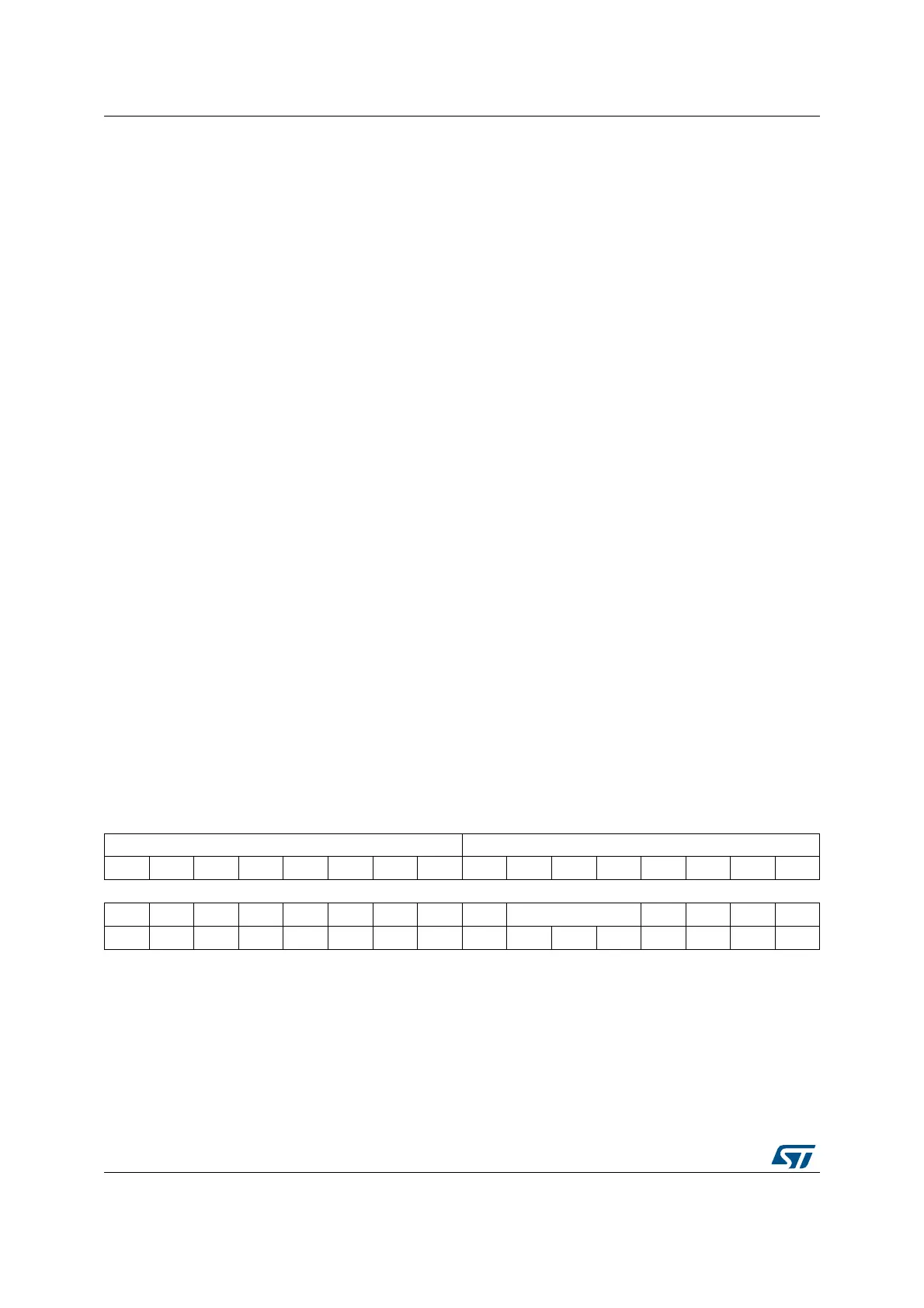

CAN error status register (CAN_ESR)

Address offset: 0x18

Reset value: 0x0000 0000

Bit 8 EWGIE: Error warning interrupt enable

0: ERRI bit will not be set when EWGF is set.

1: ERRI bit will be set when EWGF is set.

Bit 7 Reserved, must be kept at reset value.

Bit 6 FOVIE1

: FIFO overrun interrupt enable

0: No interrupt when FOVR is set.

1: Interrupt generation when FOVR is set.

Bit 5 FFIE1: FIFO full interrupt enable

0: No interrupt when FULL bit is set.

1: Interrupt generated when FULL bit is set.

Bit 4 FMPIE1

: FIFO message pending interrupt enable

0: No interrupt generated when state of FMP[1:0] bits are not 00b.

1: Interrupt generated when state of FMP[1:0] bits are not 00b.

Bit 3 FOVIE0

: FIFO overrun interrupt enable

0: No interrupt when FOVR bit is set.

1: Interrupt generated when FOVR bit is set.

Bit 2 FFIE0

: FIFO full interrupt enable

0: No interrupt when FULL bit is set.

1: Interrupt generated when FULL bit is set.

Bit 1 FMPIE0

: FIFO message pending interrupt enable

0: No interrupt generated when state of FMP[1:0] bits are not 00b.

1: Interrupt generated when state of FMP[1:0] bits are not 00b.

Bit 0 TMEIE: Transmit mailbox empty interrupt enable

0: No interrupt when RQCPx bit is set.

1: Interrupt generated when RQCPx bit is set.

Note: Refer to Section 30.8: bxCAN interrupts.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

REC[7:0] TEC[7:0]

rrrrrrrrrrrrrrrr

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. LEC[2:0] Res. BOFF EPVF EWGF

rw rw rw r r r

Loading...

Loading...