Error Correction Status Module (ECSM)

PXN20 Microcontroller Reference Manual, Rev. 1

19-2 Freescale Semiconductor

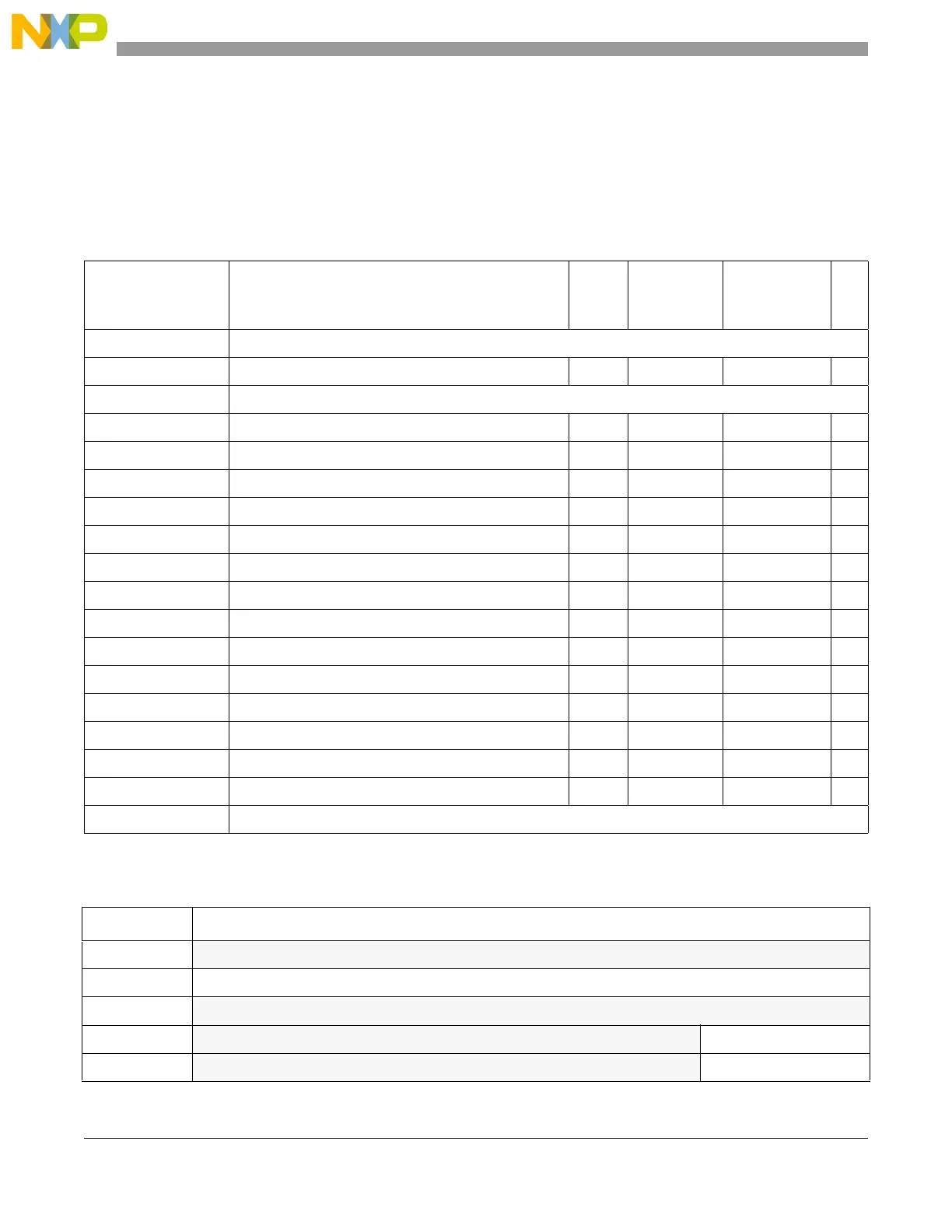

19.2.1 Module Memory Map

The ECSM memory map is shown in Table 19-1 (a graphical layout of the registers is shown in Table 19-2

to better see Reserved areas in the memory map). The address of each register is given as an offset to the

ECSM base address. Registers are listed in address order, identified by complete name and mnemonic, and

lists the type of accesses allowed.

Table 19-1. ECSM Memory Map

Offset from

ECSM_BASE_ADDR

(0xFFF4_0000)

Register Access Reset Value

1

1

Please refer to the register definition. U = undefined at reset.

Section/Page

Size

0x0000–0x0023 Reserved

0x0024

FBOMCR—FEC burst optimization master control register

R/W 0x0000_0000 19.2.2.1/19-3 32

0x0028–0x0042 Reserved

0x0043 ECR—ECC configuration register R/W 0x00 19.2.2.2/19-5 8

0x0047 ESR—ECC status register R/W 0x00 19.2.2.3/19-6 8

0x004A EEGR—ECC error generation register R/W 0x0000 19.2.2.4/19-7 16

0x0050 PFEAR—PFlash ECC address register RO U 19.2.2.5/19-9 32

0x0056 PFEMR—PFlash ECC master register RO 0x0U 19.2.2.6/19-10 8

0x0057 PFEAT—PFlash ECC attributes register RO U 19.2.2.7/19-10 8

0x0058 PFEDRH—PFlash ECC data register high RO U 19.2.2.8/19-11 32

0x005C PFEDRL—PFlash ECC data register low RO U 19.2.2.8/19-11 32

0x0060 PREAR—PRAM ECC address register RO U 19.2.2.9/19-12 32

0x0065 PRESR—PRAM ECC syndrome register RO U 19.2.2.10/19-13 8

0x0066 PREMR—PRAM ECC master register RO 0x0U 19.2.2.11/19-14 8

0x0067 PREAT—PRAM ECC attributes register RO U 19.2.2.12/19-15 8

0x0068 PREDRH—PRAM ECC data register high RO U 19.2.2.13/19-16 32

0x006C PREDRL—PRAM ECC data register low RO U 19.2.2.13/19-16 32

0x0007–0x3FFF Reserved

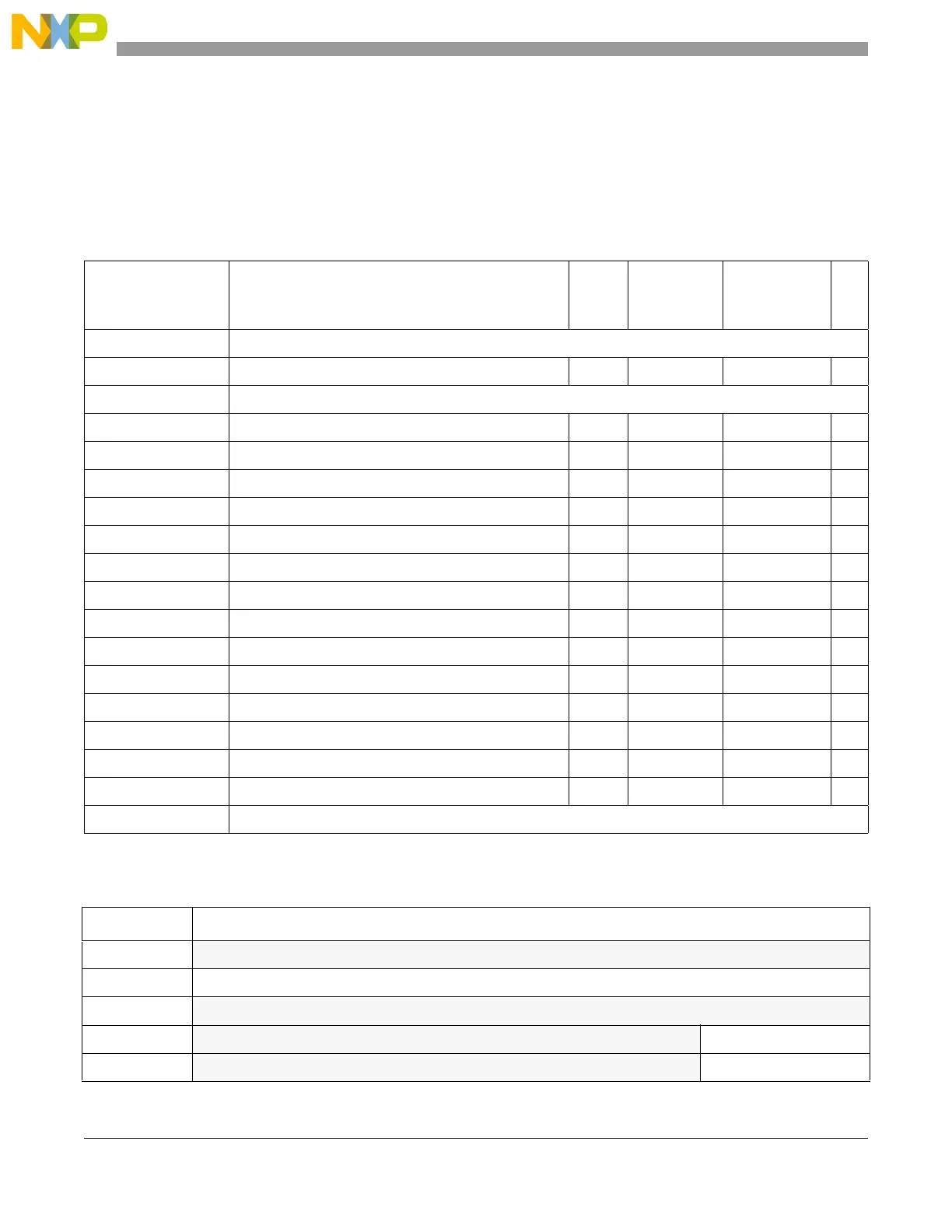

Table 19-2. ECSM Graphical Memory Map

ECSM Offset

Register

0x0000–0x0023

Reserved

0x0024 FEC burst optimization master control register (FBOMCR)

0x0028–0x003F

Reserved

0x0040 Reserved ECC configuration (ECR)

0x0044 Reserved

ECC status register (ESR)

Loading...

Loading...