Enhanced Modular Input/Output Subsystem (eMIOS200)

PXN20 Microcontroller Reference Manual, Rev. 1

28-58 Freescale Semiconductor

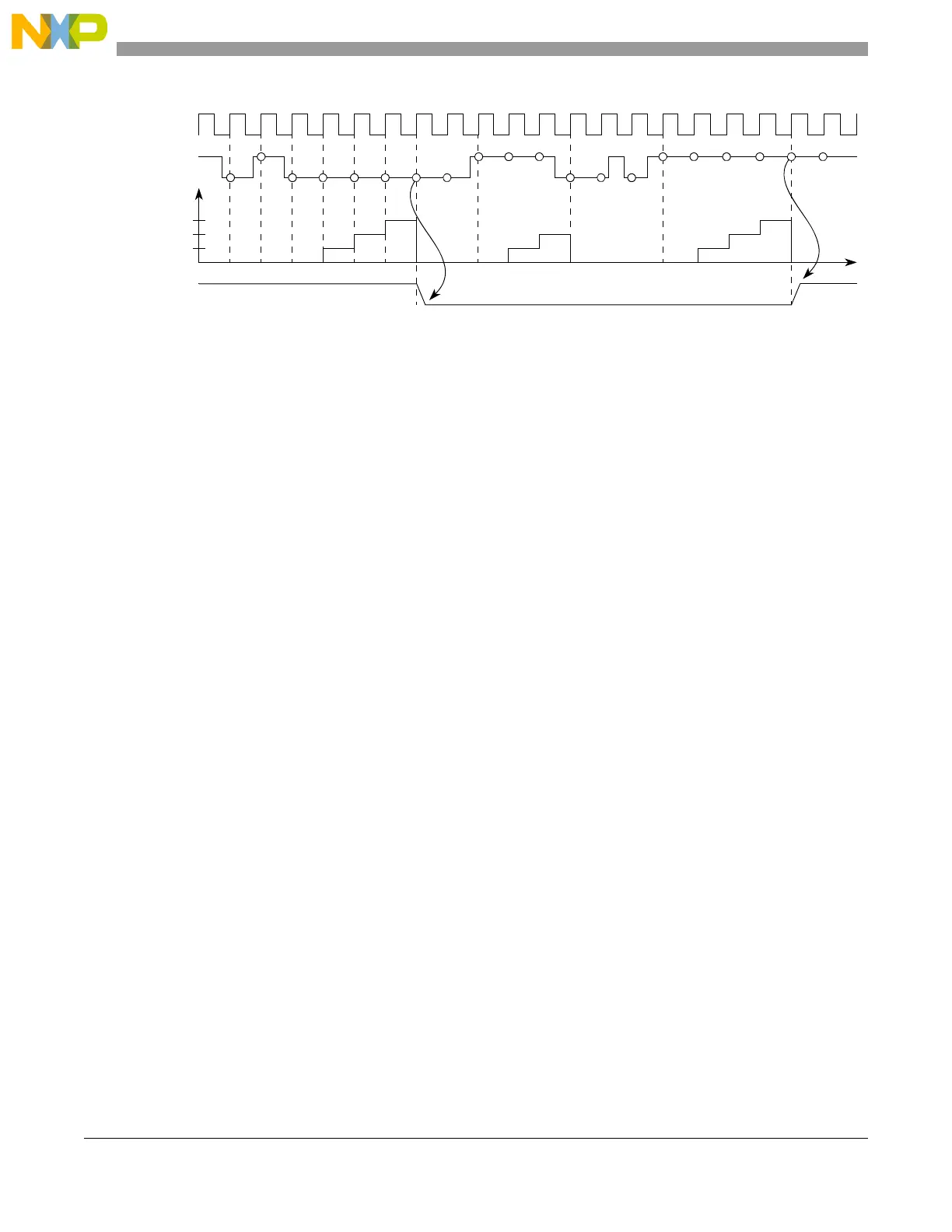

Figure 28-56. Input Programmable Filter Example

28.4.1.3 Clock Prescaler (CP)

The CP divides the GCP output signal to generate a clock enable for the internal counter of the unified

channels. It is a programmable 2-bit down counter. The GCP output signal is prescaled by the value

defined in the UCPRE bits in the EMIOS_CCR[n] register. The output is clocked every time the counter

reaches zero. Counting is enabled by setting the UCPREN bit in the EMIOS_CCR[n]. The counter can be

stopped at any time by clearing this bit, thereby stopping the internal counter in the unified channel.

In order to ensure safe working and avoid glitches the following steps must be performed whenever any

update in the prescaling rate is desired:

1. Write 0 at both GPREN bit in EMIOSMCR register and UCPREN bit in EMIOS_CCR[n] register,

thus disabling prescalers;

2. Write the desired value for prescaling rate at UCPRE[] bits in EMIOS_CCR[n] register;

3. Enable channel prescaler by writing 1 at UCPREN bit in EMIOS_CCR[n] register;

4. Enable global prescaler by writing 1 at GPREN bit in EMIOSMCR register.

The prescaler is not disabled during either freeze state or negated GTBE input.

28.4.1.4 Effect of Freeze on the Unified Channel

When in debug mode, if the FRZ bit in the EMIOS_MCR register and the FREN bit in the

EMIOS_CCR[n] are both set, the internal counter and unified channel capture and compare functions are

halted. The unified channel is frozen in its current state.

During freeze, all registers are accessible. When the unified channel is operating in an output mode, the

force match functions remain available, allowing the software to force the output to the desired level.

During input modes, any input events that may occur while the channel is frozen are ignored.

When exiting debug mode or when the freeze enable bit is cleared (FRZ in the EMIOS_MCR or FREN in

the EMIOS_CCR[n] register), the channel actions resume but may be inconsistent until the channel enters

GPIO mode again.

Selected Clock

5-bit Counter

Filter Out

EMIOSI

Time

Loading...

Loading...