PXN20 Microcontroller Reference Manual, Rev. 1

Freescale Semiconductor 24-1

Chapter 24

Enhanced Direct Memory Access Controller (eDMA)

24.1 Introduction

The enhanced direct memory access controller (eDMA) is a second-generation platform block capable of

performing complex data movements through 32 programmable channels, with minimal intervention from

the host processor. The hardware microarchitecture includes a DMA engine that performs source and

destination address calculations, and the actual data movement operations, along with an SRAM-based

memory containing the transfer control descriptors (TCD) for the channels. This implementation

minimizes the overall block size.

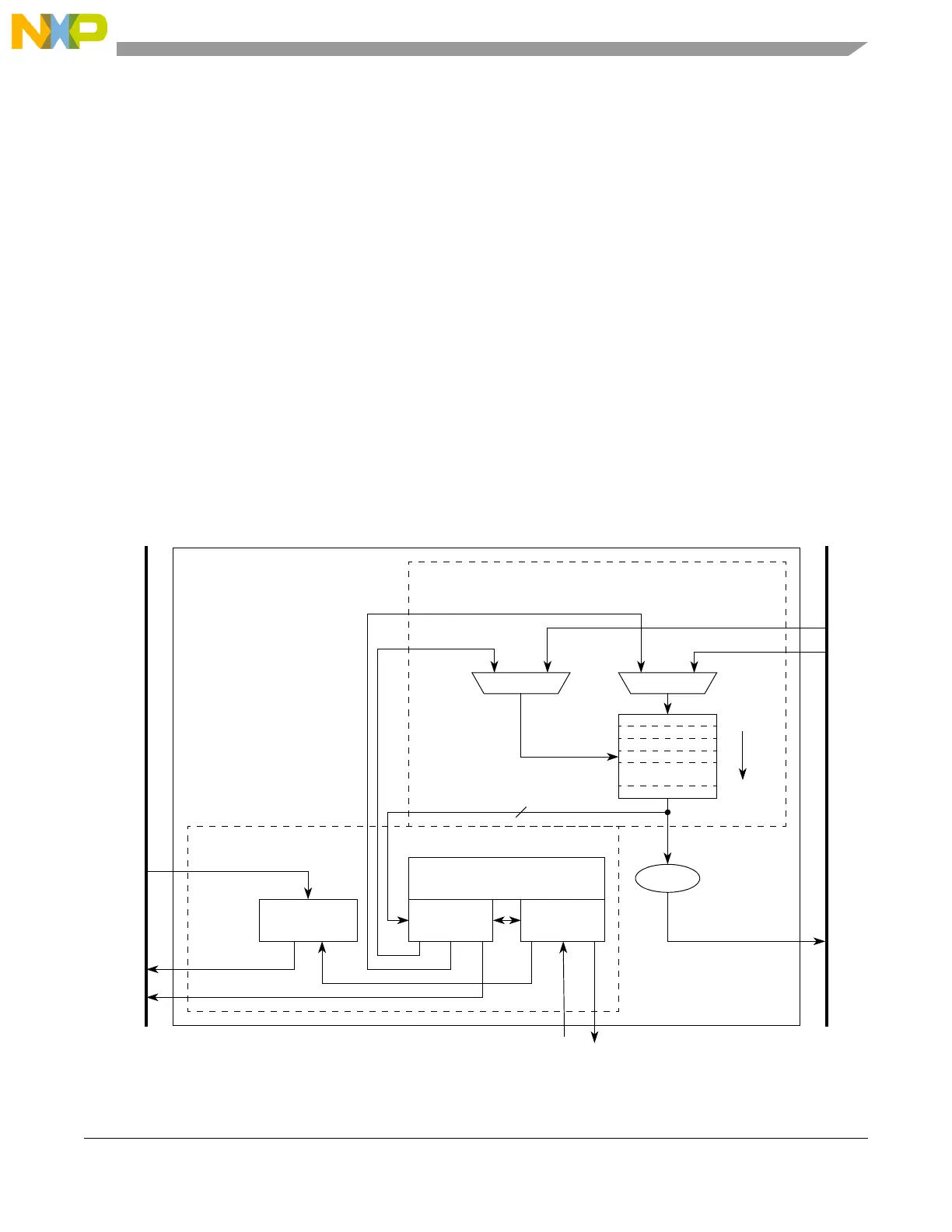

24.1.1 Block Diagram

Figure 24-1 shows a simplified block diagram of the eDMA.

Figure 24-1. eDMA Block Diagram

Slave interface

eDMA

eDMA Done

System bus

Data path

Control

Address

Program model/

Slave write data

Slave write address

Bus write data

Slave read data

Bus address

eDMA engine

TCD0

TCDn-1*

eDMA Peripheral Request

Bus read data

channel arbitration

path

SRAM

transfer control descriptor

(TCD)

SRAM

*n = 32 channels

Loading...

Loading...