FlexRay Communication Controller (FlexRAY)

PXN20 Microcontroller Reference Manual, Rev. 1

Freescale Semiconductor 26-89

26.6.5.2 Message Buffer Header Field Description

This section provides a detailed description of the usage and content of the message buffer header field. A

description of the structure of the message buffer header fields is given in Section 26.6.2.1, Message

Buffer Header Field. Each message buffer header field consists of three sections: the frame header section,

the data field offset, and the slot status section. For a detailed description of the Data Field Offset, see

Section 26.6.2.1.2, Data Field Offset.

26.6.5.2.1 Frame Header Description

Frame Header Content

The semantic and content of the frame header section depends on the message buffer type.

For individual receive message buffers and receive FIFOs, the frame header receives the frame header data

of the first valid frame received on the assigned channels.

For receive shadow buffers, the frame header receives the frame header data of the current frame received

regardless of whether the frame is valid or not.

For transmit message buffers, the application writes the frame header of the frame to be transmitted into

this location. The frame header will be read out when the frame is transferred to the FlexRay bus.

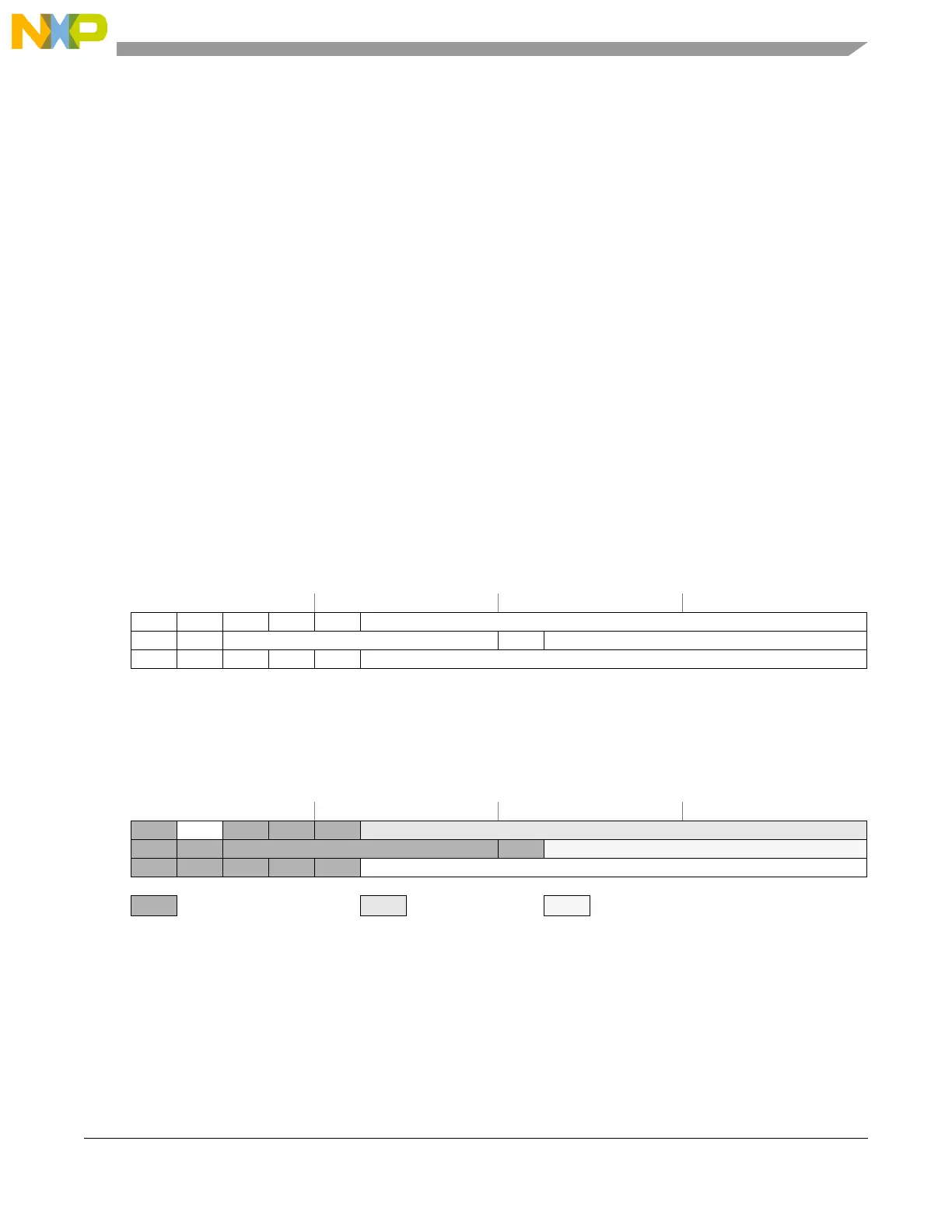

The structure of the frame header in the message buffer header field for receive message buffers and the

receive FIFO is given in Figure 26-109. A detailed description is given in Table 26-85.

Figure 26-109. Frame Header Structure (Receive Message Buffer and Receive FIFO)

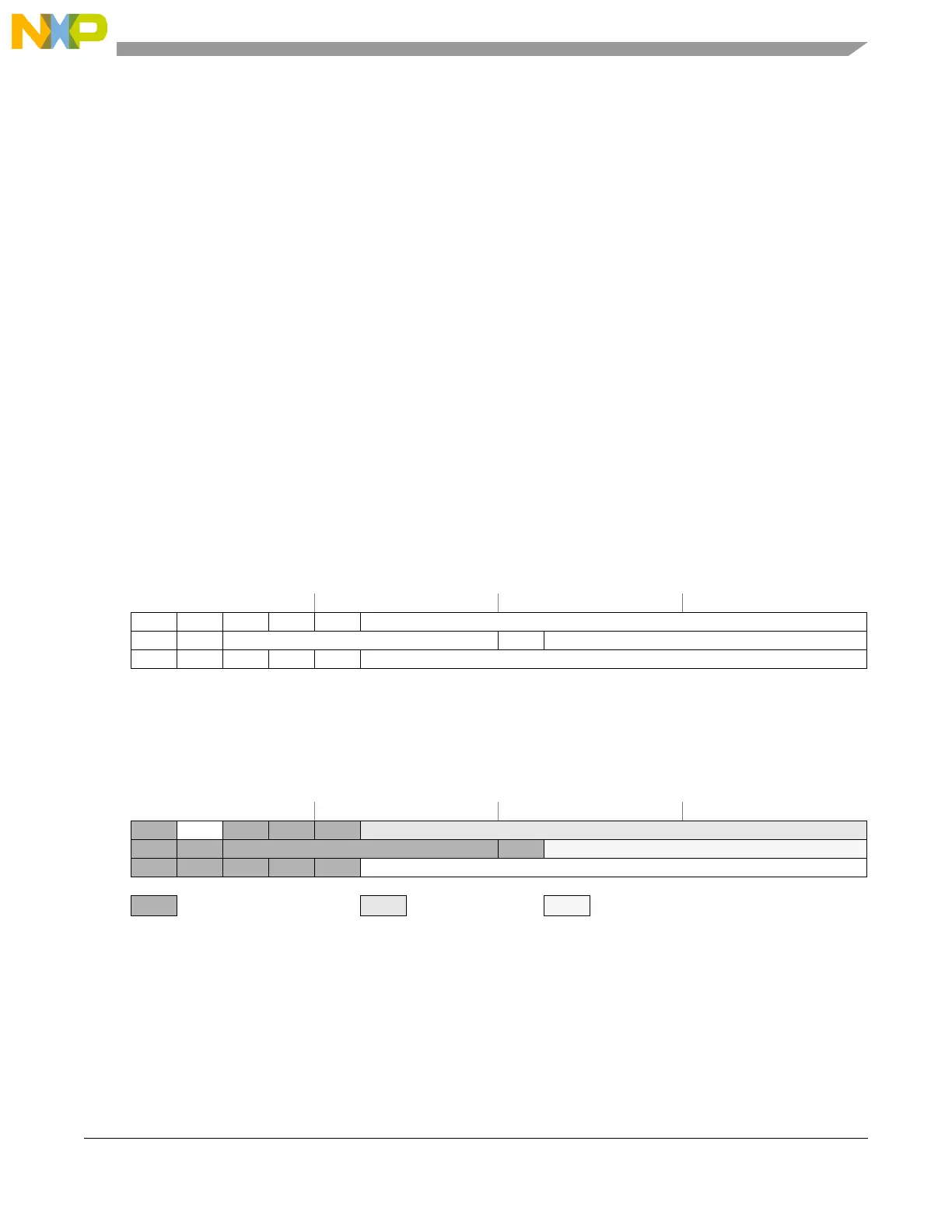

The structure of the frame header in the message buffer header field for transmit message buffers is given

in Figure 26-110. A detailed description is given in Table 26-86. The checks that will be performed are

described in Frame Header Checks.

Figure 26-110. Frame Header Structure (Transmit Message Buffer)

The structure of the frame header in the message buffer header field for transmit message buffers assigned

to key slot is given in Figure 26-111.

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

0x0 R PPI NUF SYF SUF FID

0x2 0 0 CYCCNT 0 PLDLEN

0x400000 HDCRC

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

0x0 R PPI NUF SYF SUF FID

0x2 CYCCNT PLDLEN

0x4 HDCRC

= not used

= checked = checked if static slot

Loading...

Loading...