RM0016 General purpose I/O ports (GPIO)

Doc ID 14587 Rev 8 113/449

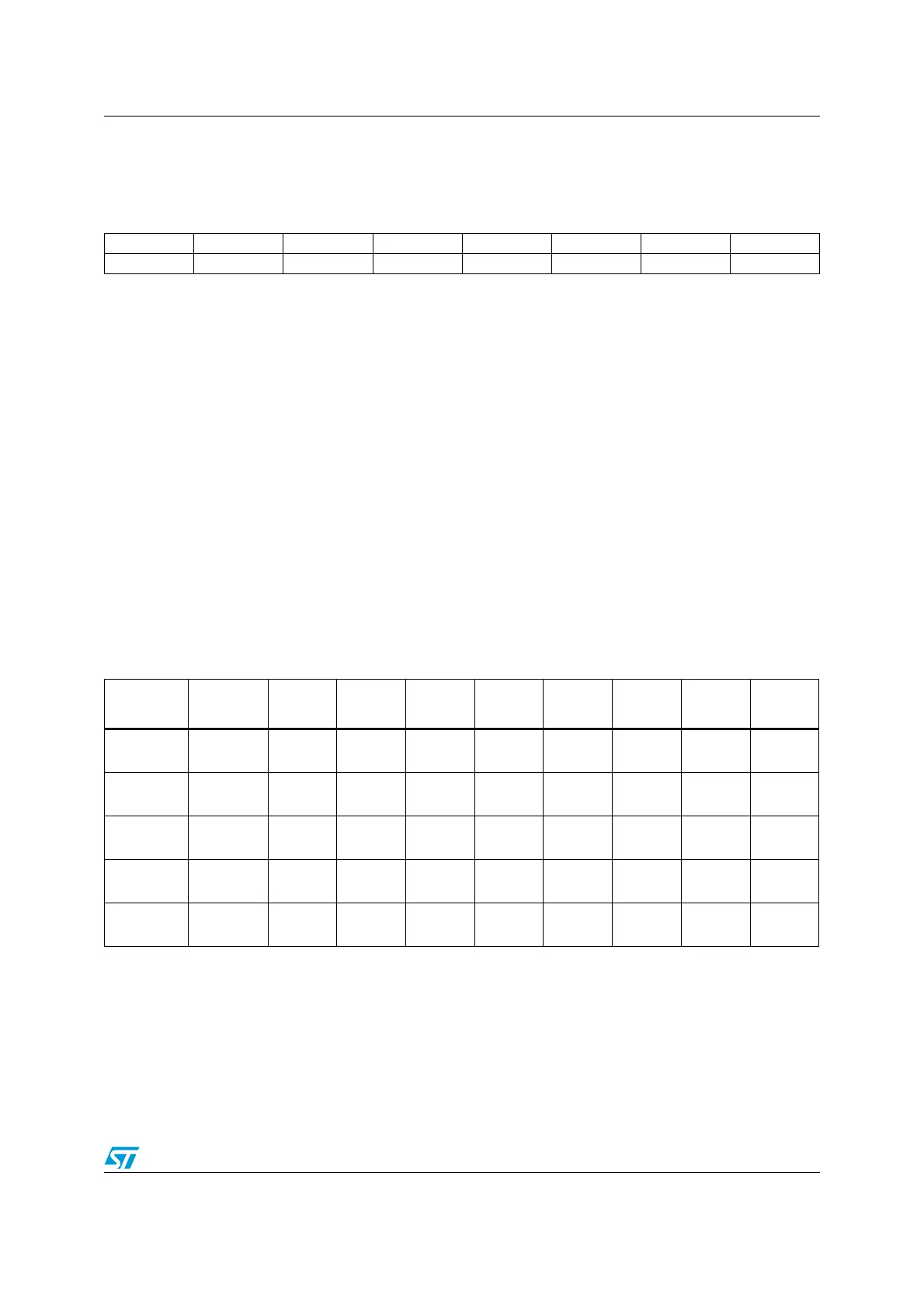

11.9.5 Port x control register 2 (Px_CR2)

Address offset: 0x04

Reset value: 0x00

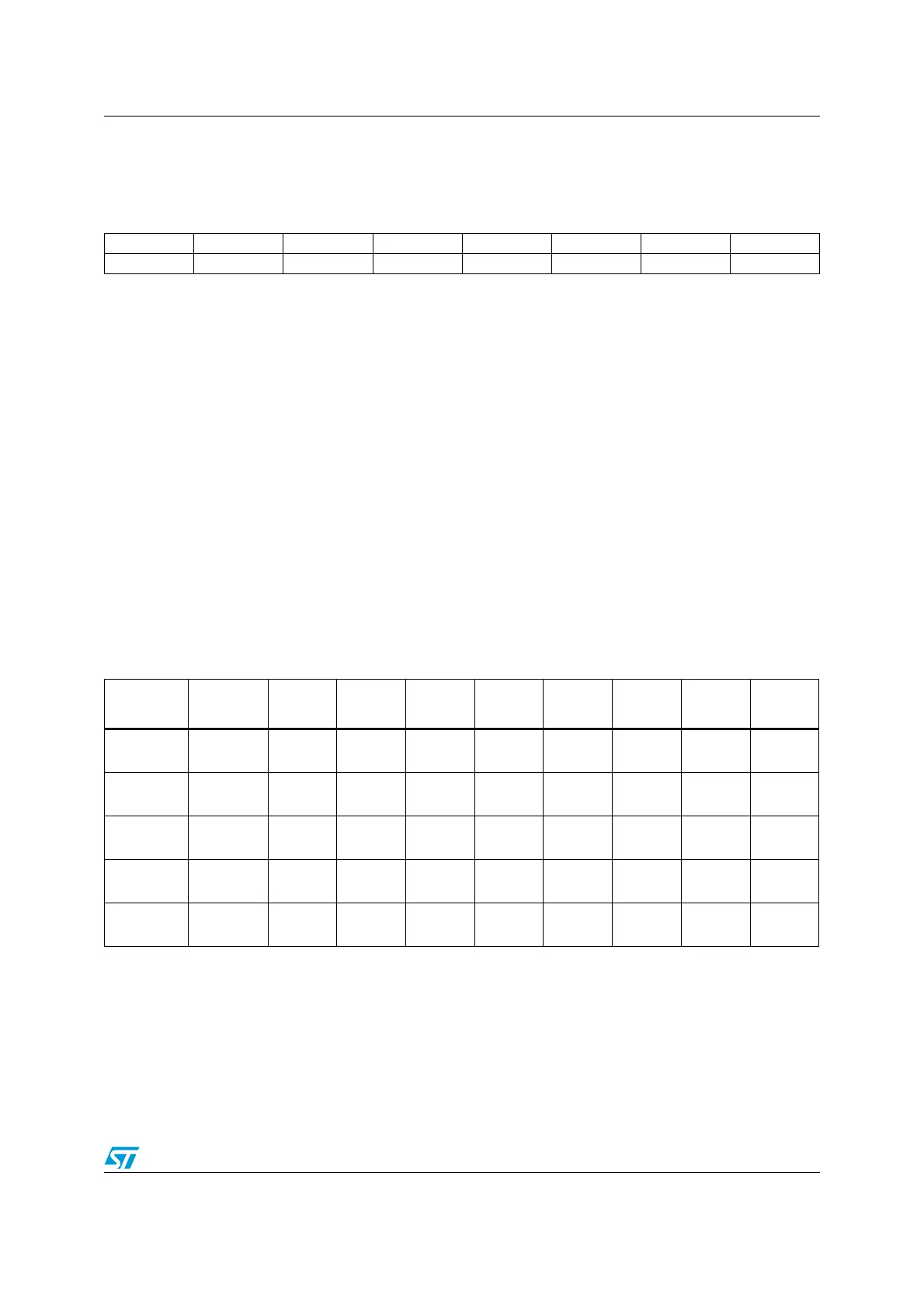

11.9.6 GPIO register map and reset values

Each GPIO port has five registers mapped as shown in Ta bl e 24 . Refer to the register map

in the corresponding datasheet for the base address for each port.

Note: At reset state, all ports are input floating. Exceptions are indicated in the pin description

table of the corresponding datasheet.

76543210

C27 C26 C25 C24 C23 C22 C21 C20

rw rw rw rw rw rw rw rw

Bits 7:0 C2[7:0]: Control bits

These bits are set and cleared by software. They select different functions in input mode and output

mode. In input mode, the CR2 bit enables the interrupt capability if available. If the I/O does not have

interrupt capability, setting the CR2 bit has no effect. In output mode, setting the bit increases the

speed of the I/O. This applies to ports with O3 and O4 output types (see pin description table).

– In input mode (DDR = 0):

0: External interrupt disabled

1: External interrupt enabled

– In output mode (DDR = 1):

0: Output speed up to 2 MHz

1: Output speed up to 10 MHz

Table 24. GPIO register map

Address

offset

Register

name

76543210

0x00 Px_ODR

ODR7

0

ODR6

0

ODR5

0

ODR4

0

ODR3

0

ODR2

0

ODR1

0

ODR0

0

0x01 Px_IDR

IDR7

x

IDR6

x

IDR5

x

IDR4

x

IDR3

x

IDR2

x

IDR1

x

IDR0

x

0x02 Px_DDR

DDR7

0

DDR6

0

DDR5

0

DDR4

0

DDR3

0

DDR2

0

DDR1

0

DDR0

0

0x03 Px_CR1

(1)

C17

0

C16

0

C15

0

C14

0

C13

0

C12

0

C11

0

C10

0

0x04 Px_CR2

C27

0

C26

0

C25

0

C24

0

C23

0

C22

0

C21

0

C20

0

1. PD_CR reset value is 0x02.

Loading...

Loading...