RM0016 Analog/digital converter (ADC)

Doc ID 14587 Rev 8 427/449

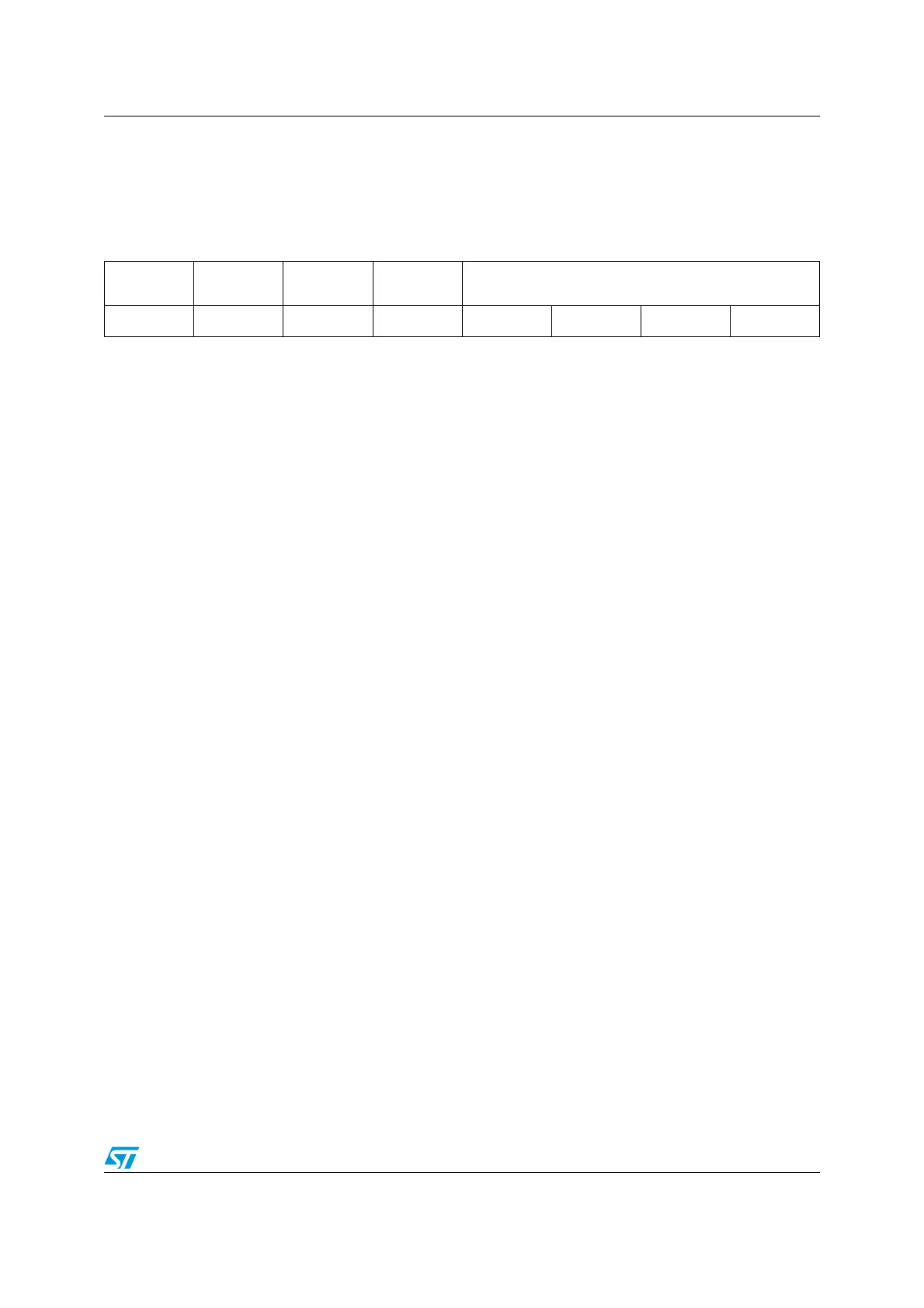

24.11.3 ADC control/status register (ADC_CSR)

Address offset: 0x20

Reset value: 0x00

76543210

EOC AWD EOCIE AWDIE CH[3:0]

rw rc_w0 rw rw rw rw rw rw

Bit 7 EOC: End of conversion

This bit is set by hardware at the end of conversion. It is cleared by software by

writing ‘0’.

0: Conversion is not complete

1: Conversion complete

Bit 6 AWD: Analog Watchdog flag

0: No analog watchdog event

1: An analog watchdog event occurred. In buffered continuous or scan mode

you can read the ADC_AWSR register to determine the data buffer register

related to the event. An interrupt request is generated if AWDIE=1.

Note: This bit is not available for ADC2

Bit 5 EOCIE: Interrupt enable for EOC

This bit is set and cleared by software. It enables the interrupt for End of

Conversion.

0: EOC interrupt disabled

1: EOC interrupt enabled. An interrupt is generated when the EOC bit is set.

Bit 4 AWDIE: Analog watchdog interrupt enable

0: AWD interrupt disabled.

1: AWD interrupt enabled

Note: This bit is not available for ADC2

Bits 3:0 CH[3:0]: Channel selection bits

These bits are set and cleared by software. They select the input channel to be

converted.

0000: Channel AIN0

0001: Channel AIN1

....

1111: Channel AIN15

Loading...

Loading...