Controller area network (beCAN) RM0016

394/449 Doc ID 14587 Rev 8

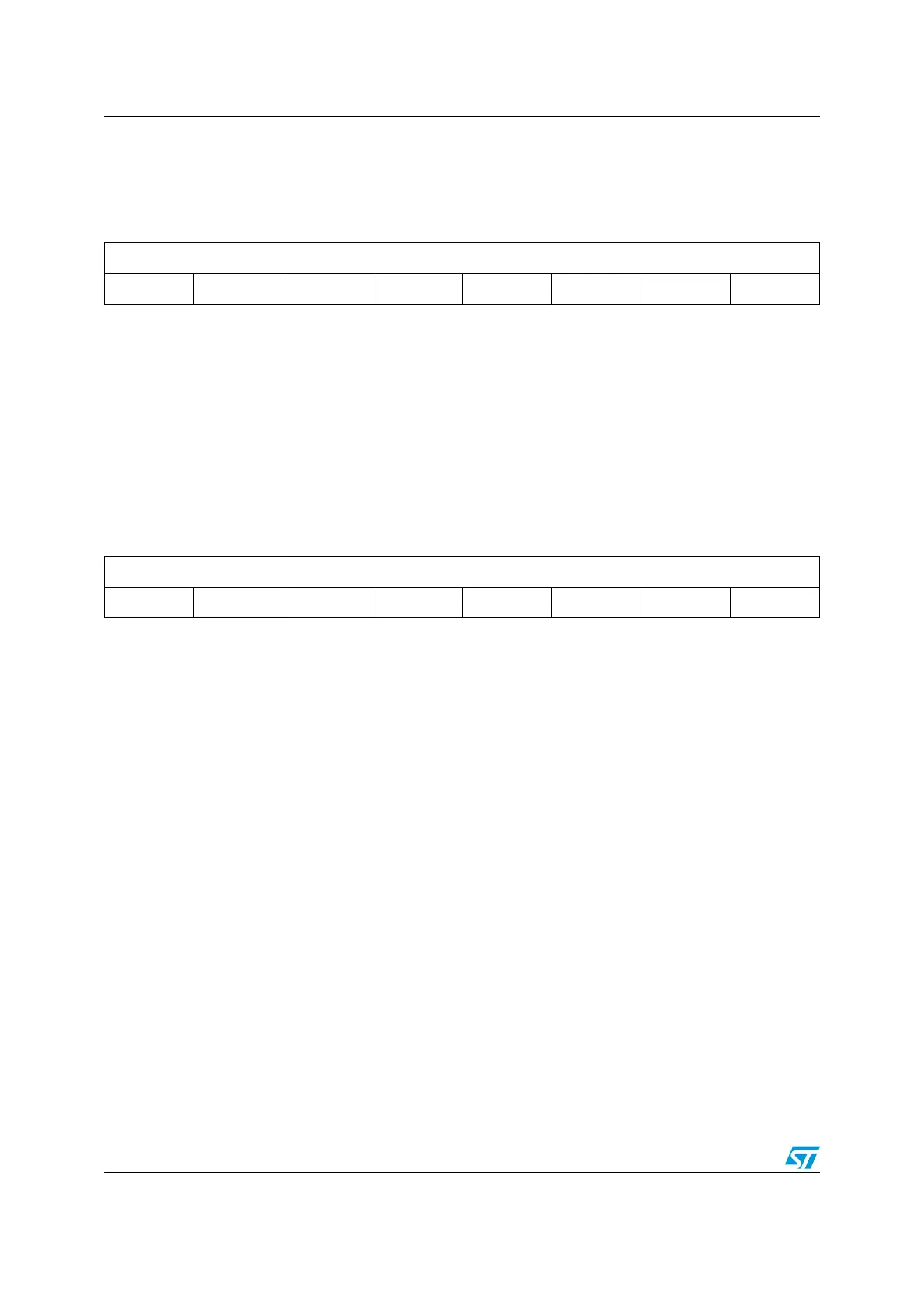

23.11.12 CAN receive error counter register (CAN_RECR)

Address offset: See Table 70.

Reset value: 0000 0000 (00h)

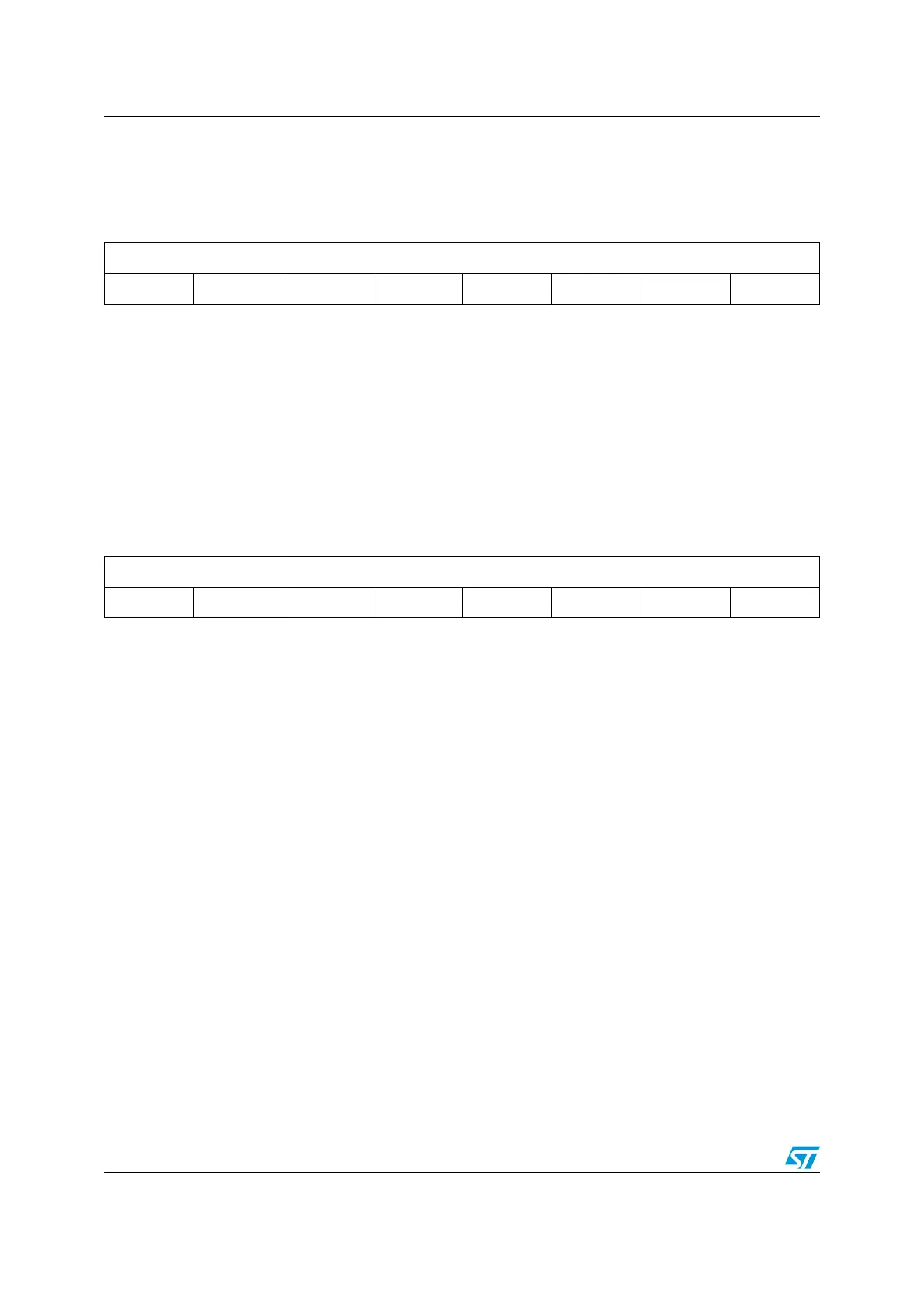

23.11.13 CAN bit timing register 1 (CAN_BTR1)

Address offset: See Table 70.

Reset value: 0100 0000 (40h)

This register can only be accessed by the software when the CAN hardware is in

initialization mode.

76543210

REC[7:0]

rrrrrrrr

Bits 7:0 REC[7:0] Receive error counter

This is the Receive Error Counter implementing part of the fault confinement mechanism of the CAN

protocol. In case of an error during reception, this counter is incremented by 1 or by 8 depending on

the error condition as defined by the CAN standard. After every successful reception the counter is

decremented by 1 or reset to 120 if its value was higher than 128. When the counter value exceeds

127, the CAN controller enters the error passive state.

76543210

SJW[1:0] BRP[5:0]

rw rw rw rw rw rw rw rw

Bits 7:6 SJW[1:0] Resynchronization jump width

These bits define the maximum number of time quanta the CAN hardware is allowed to lengthen or

shorten a bit to perform the resynchronization. Resynchronization Jump Width = (SJW+1).

Bits 5:0 BRP[5:0] Baud rate prescaler

These bits define the length of a time quantum.

tq = (BRP+1)/f

MASTER

Loading...

Loading...