16-bit general purpose timers (TIM2, TIM3, TIM5) RM0016

236/449 Doc ID 14587 Rev 8

18.6.14 Counter low (TIMx_CNTRL)

Address offset: 0x0B or 0x0D (TIM2), 0x09 (TIM3), 0x0D (TIM5); for TIM2 address see

Section

Reset value: 0x00

18.6.15 Prescaler register (TIMx_PSCR)

Address offset: 0x0C or 0x0E (TIM2), 0x0A (TIM3), 0x0E (TIM5); for TIM2 address see

Section

Reset value: 0x00

18.6.16 Auto-reload register high (TIMx_ARRH)

Address offset: 00x0D or 0x0F (TIM2), 0x0B (TIM3), 0x0F (TIM5); for TIM2 address see

Section

Reset value: 0xFF

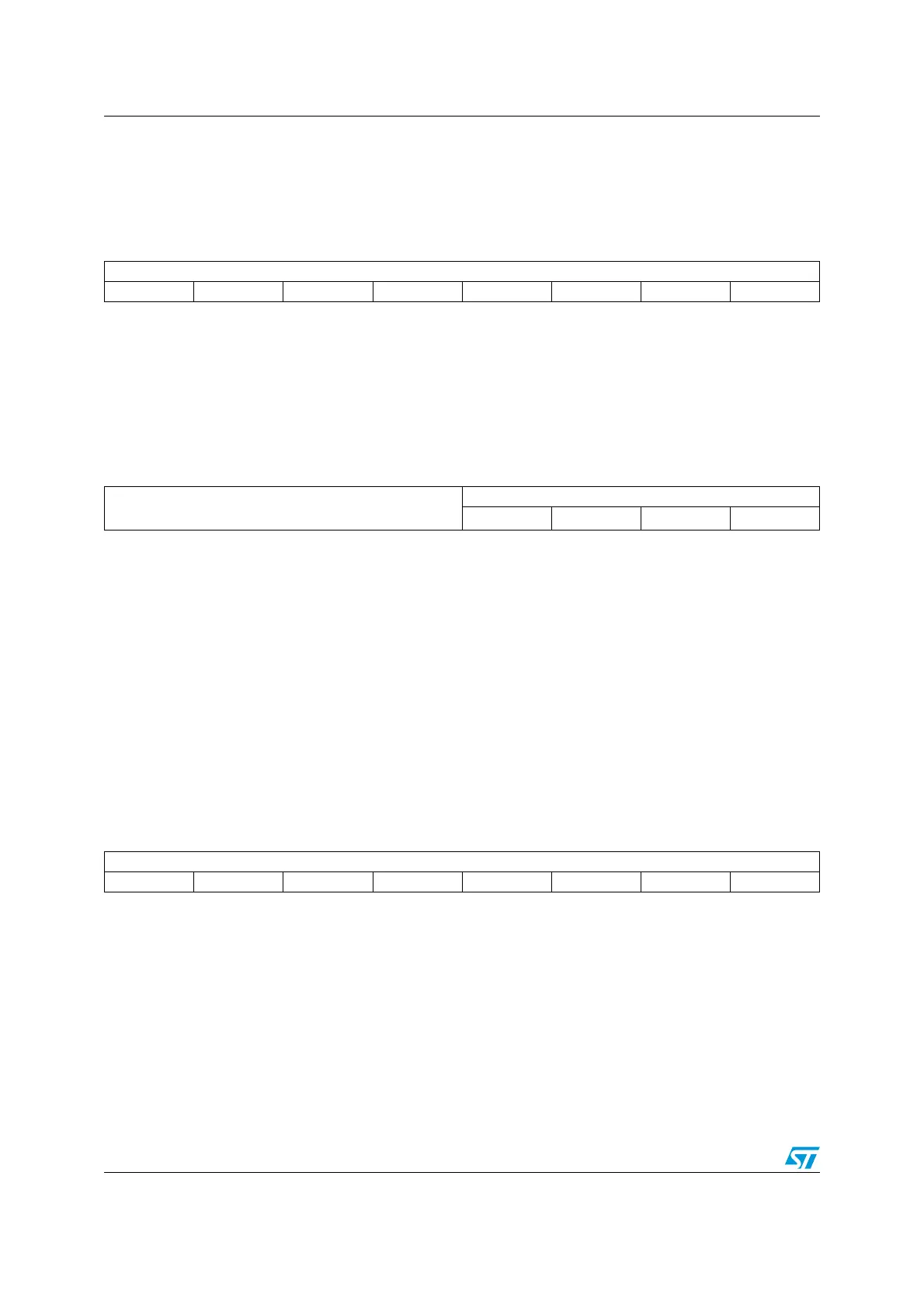

76543210

CNT[7:0]

rw rw rw rw rw rw rw rw

Bits 7:0 CNT[7:0]: Counter value (LSB)

76543210

Reserved

PSC[3:0]

rw

rw

rw rw

Bits 7:3 Reserved

Bits 2:0 PSC[3:0]: Prescaler value

The prescaler value divides the CK_PSC clock frequency.

The counter clock frequency f

CK_CNT

is equal to f

CK_PSC

/ 2

(PSC[3:0])

. PSC[7:4] are forced to 0 by

hardware.

PSCR contains the value which is loaded in the active prescaler register at each update event

(including when the counter is cleared through the UG bit of the TIMx_EGR register).

This means that a UEV must be generated so that a new prescaler value can be taken into account.

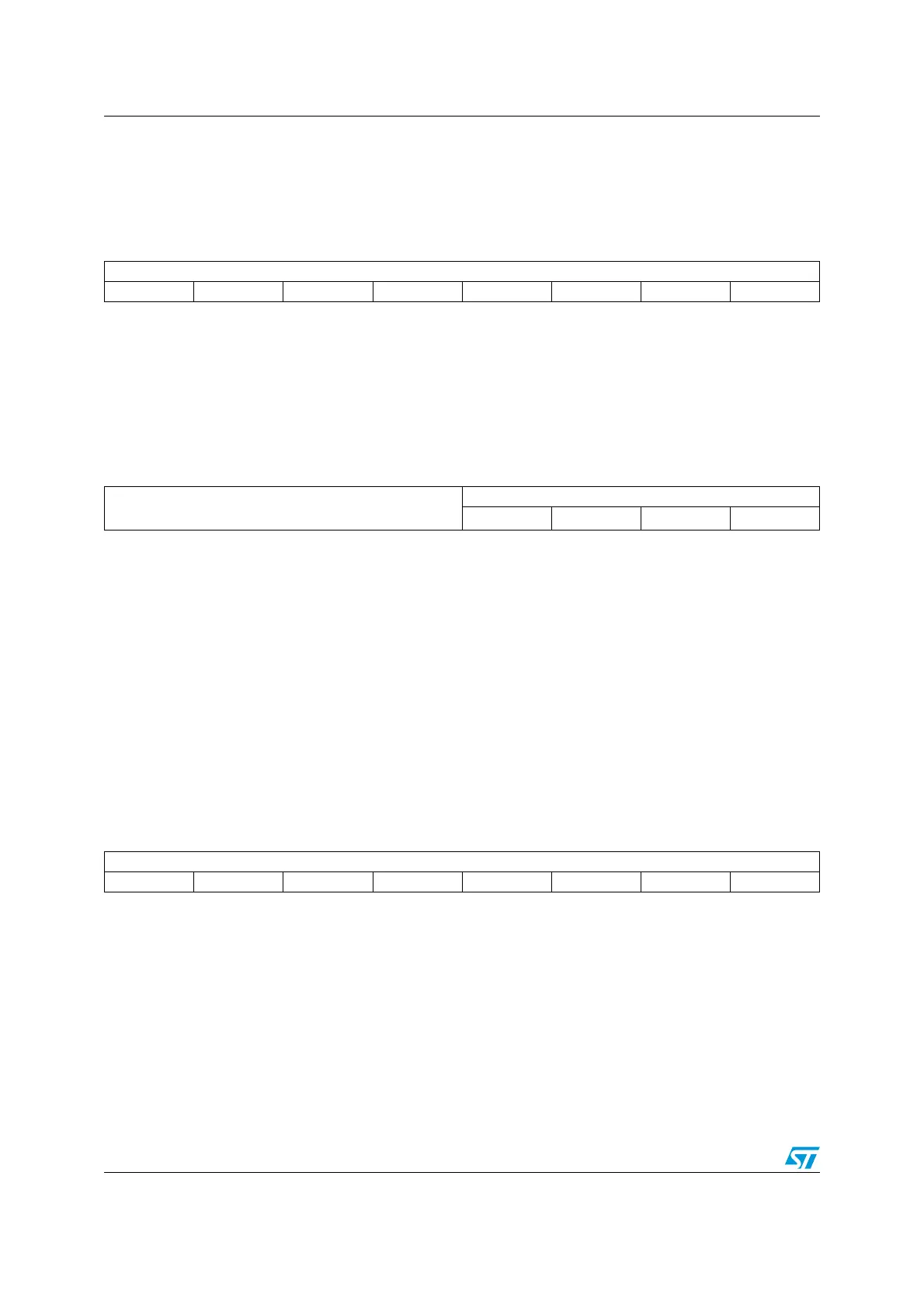

76543210

ARR[15:8]

rw rw rw rw rw rw rw rw

Bits 7:0 ARR[15:8]: Auto-reload value (MSB)

ARR is the value to be loaded in the actual auto-reload register.

Refer to the Section 17.3: TIM1 time base unit on page 139 for more details about ARR update and

behavior.

The counter is blocked while the auto-reload value is 0.

Loading...

Loading...