RM0016 Clock control (CLK)

Doc ID 14587 Rev 8 91/449

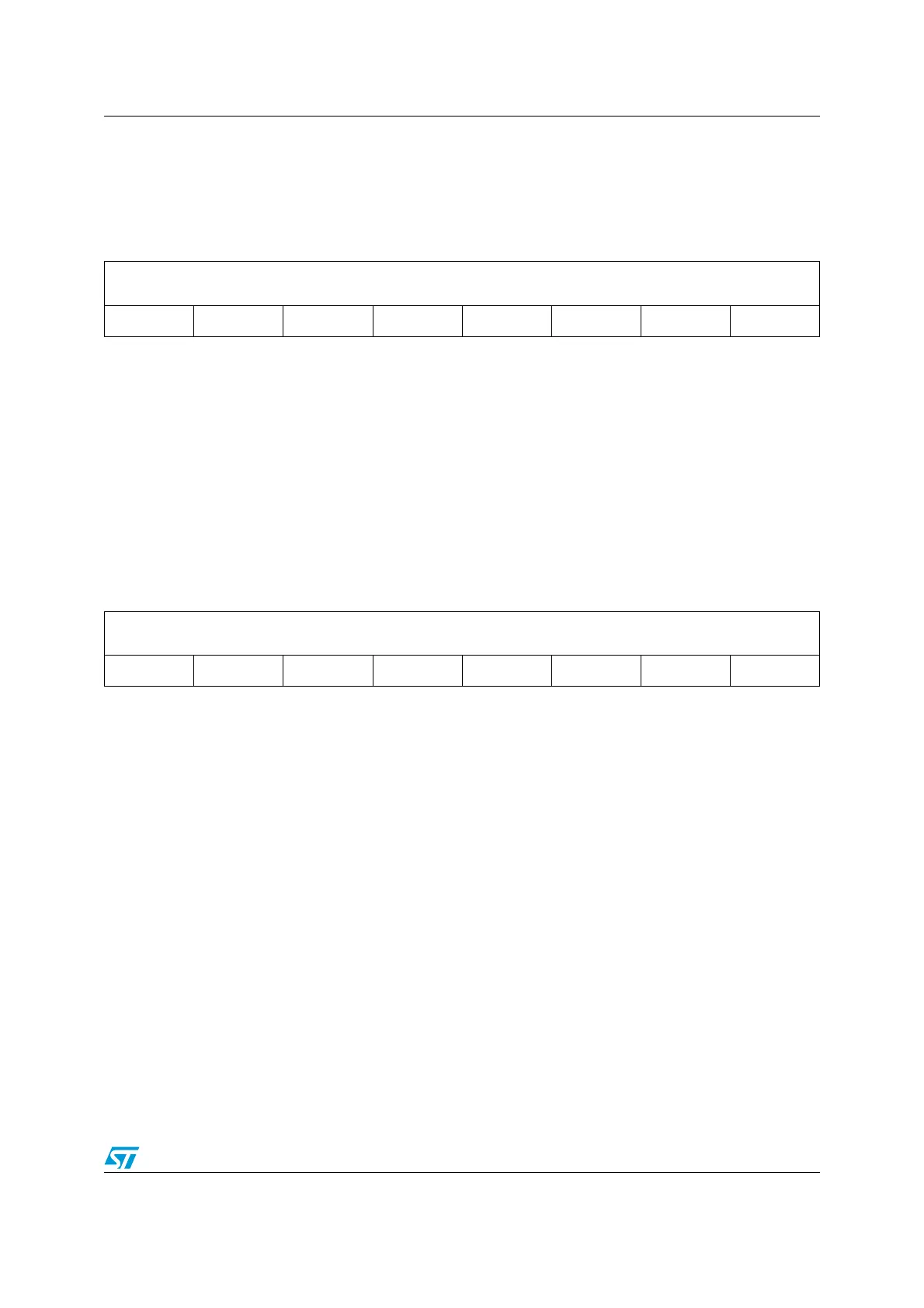

9.9.3 Clock master status register (CLK_CMSR)

Address offset:0x03

Reset value: 0xE1

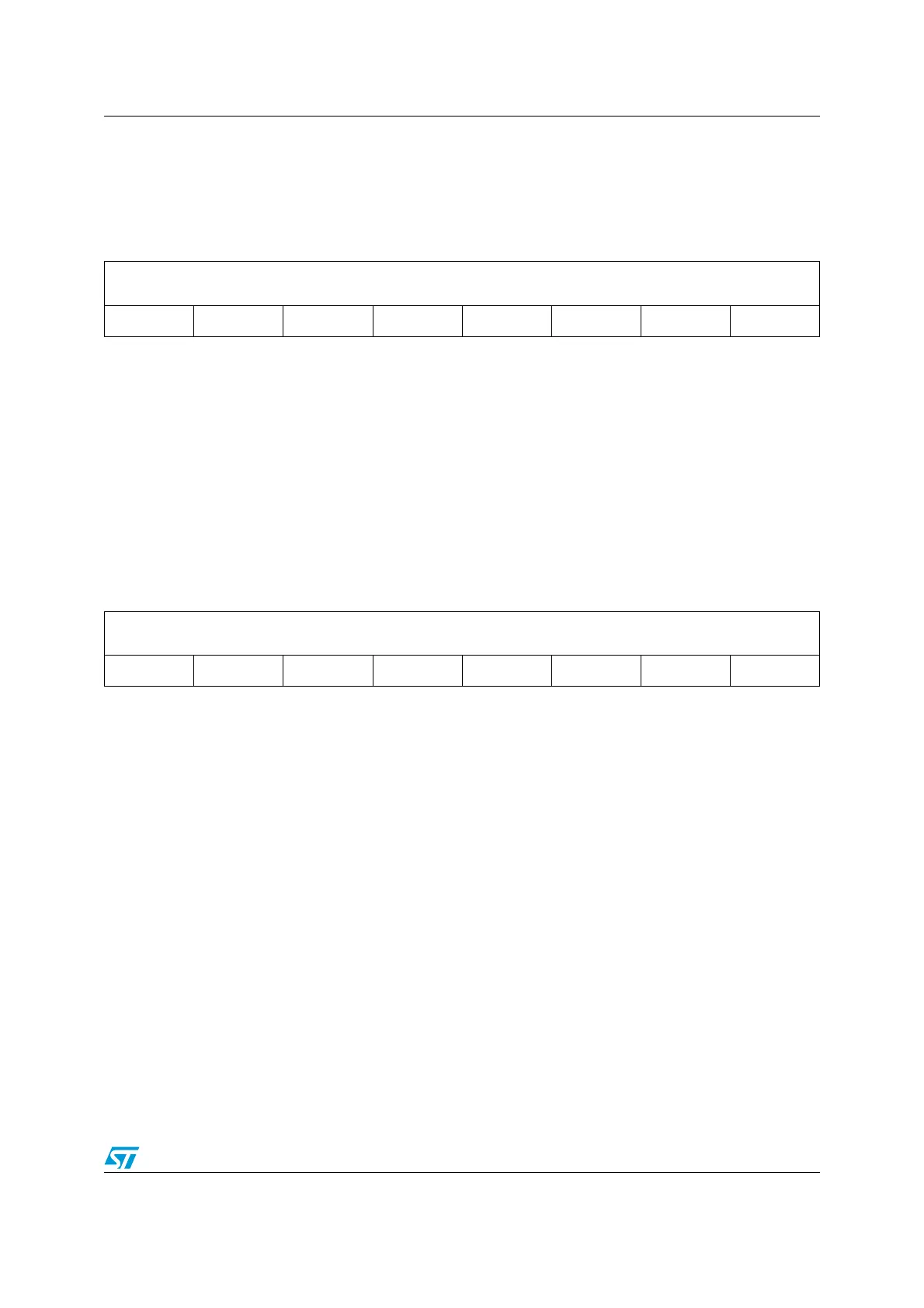

9.9.4 Clock master switch register (CLK_SWR)

Address offset: 0x04

Reset value: 0xE1

76543210

CKM[7:0]

rrrrrrrr

Bits 7:0 CKM[7:0]: Clock master status bits

These bits are set and cleared by hardware. They indicate the currently selected master clock

source. An invalid value occurring in this register will automatically generate an MCU reset.

0xE1: HSI selected as master clock source (reset value)

0xD2: LSI selected as master clock source (only if LSI_EN option bit is set)

0xB4: HSE selected as master clock source

76543210

SWI[7:0]

rw rw rw rw rw rw rw rw

Bits 7:0 SWI[7:0]: Clock master selection bits

These bits are written by software to select the master clock source. Its contents are write protected

while a clock switch is ongoing (while the SWBSY bit is set). They are set to the reset value (HSI) if

the AUX bit is set in the CLK_CSSR register. If Fast Halt wakeup mode is selected (FHW bit =1 in

CLK_ICKR register) then these bits are set by hardware to E1h (HSI selected) when resuming from

Halt/Active-halt mode.

0xE1: HSI selected as master clock source (reset value)

0xD2: LSI selected as master clock source (only if LSI_EN option bit is set)

0xB4: HSE selected as master clock source

Loading...

Loading...