Independent watchdog (IWDG) RM0016

122/449 Doc ID 14587 Rev 8

14 Independent watchdog (IWDG)

14.1 Introduction

The independent watchdog peripheral can be used to resolve processor malfunctions due to

hardware or software failures. It is clocked by the 128 kHz LSI internal RC clock source, and

thus stays active even if the main clock fails.

14.2 IWDG functional description

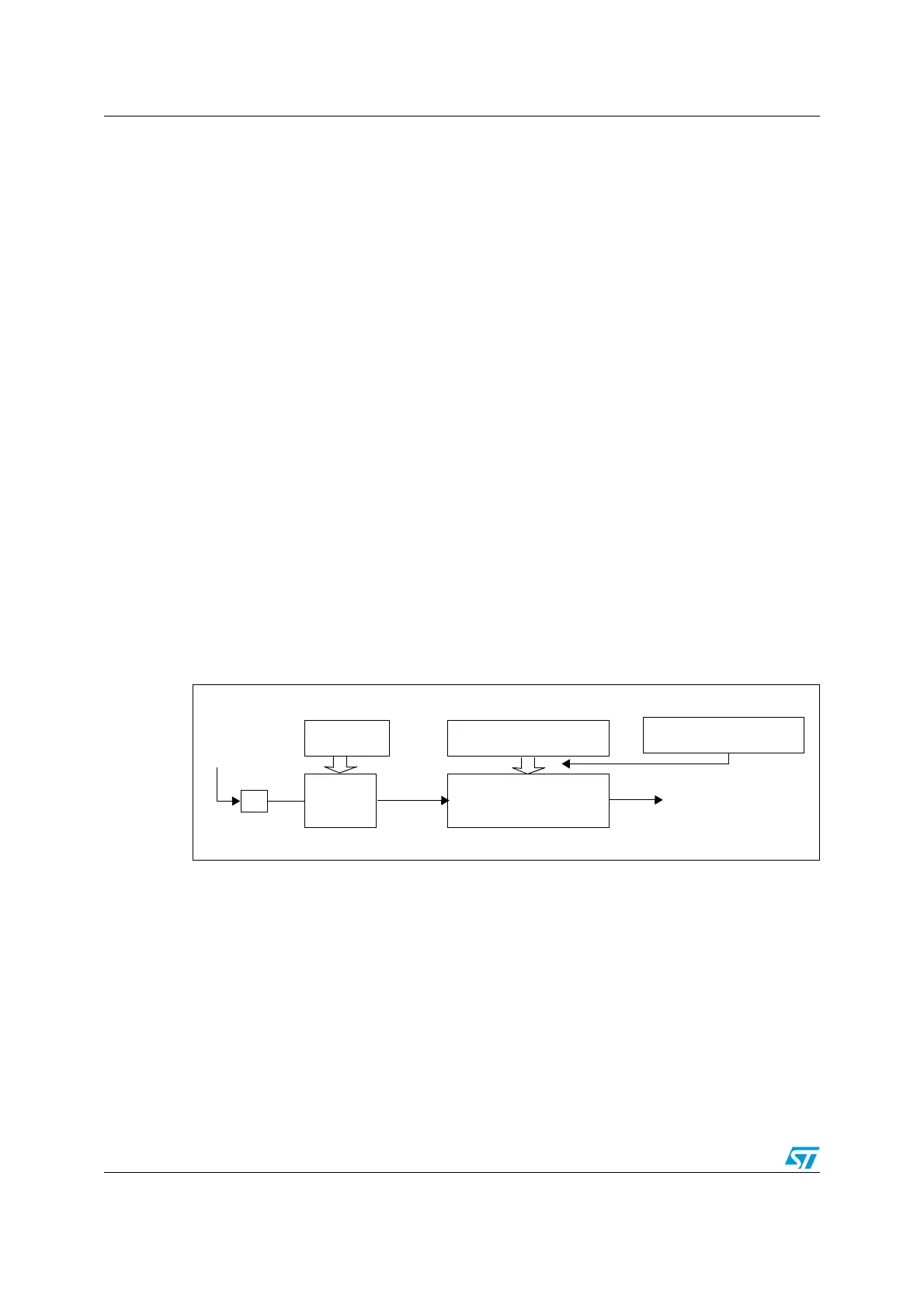

Figure 27 shows the functional blocks of the independent watchdog module.

When the independent watchdog is started by writing the value 0xCC in the key register

(IWDG_KR), the counter starts counting down from the reset value of 0xFF. When it reaches

the end of count value (0x00) a reset signal is generated (IWDG RESET).

Once enabled, the independent watchdog can be configured through the IWDG_PR, and

IWDG_RLR registers. The IWDG_PR register is used to select the prescaler divider feeding

the counter clock. Whenever the KEY_REFRESH value (0xAA) is written in the IWDG_KR

register, the IWDG is refreshed by reloading the IWDG_RLR value into the counter and the

watchdog reset is prevented.

The IWDG_PR and IWDG_RLR registers are write protected. To modify them, first write the

KEY_ACCESS code (0x55) in the IWDG_KR register. The sequence can be aborted by

writing 0xAA in the IWDG_KR register to refresh it.

Refer to Section 14.3: IWDG registers for details on the IWDG registers.

Figure 27. Independent watchdog (IWDG) block diagram

Hardware watchdog feature

If the hardware watchdog feature has been enabled through the IWDG_HW option byte, the

watchdog is automatically enabled at power-on, and generates a reset unless the key

register is written by the software before the counter reaches end of count. Refer to the

option byte description in the datasheet.

WDG reset

prescaler

8-bit down-counter

IWDG_PR

register

IWDG_RLR

reload register

7-bit

IWDG_KR

key register

128 kHz LSI

clock

64

kHz

/2

Loading...

Loading...