16-bit advanced control timer (TIM1) RM0016

164/449 Doc ID 14587 Rev 8

The capture/compare block is made of one preload register and one shadow register. Write

and read always access the preload register. In capture mode, captures are made in the

shadow register, which is copied into the preload register. In compare mode, the content of

the preload register is copied into the shadow register which is compared to the counter.

When the channel is configured in output mode (CCiS = 00 in the TIM1_CCMRi registers),

the TIM1_CCRi registers can be accessed without any restriction.

When the channel is configured in input mode, the sequence for reading the TIM1_CCRi

registers is the same as for the counter (see Figure 62). When a capture occurs, the content

of the counter is captured into the TIM1_CCRi shadow registers. Then this value is loaded

into the preload register, except during a read sequence, when the preload register is

frozen.

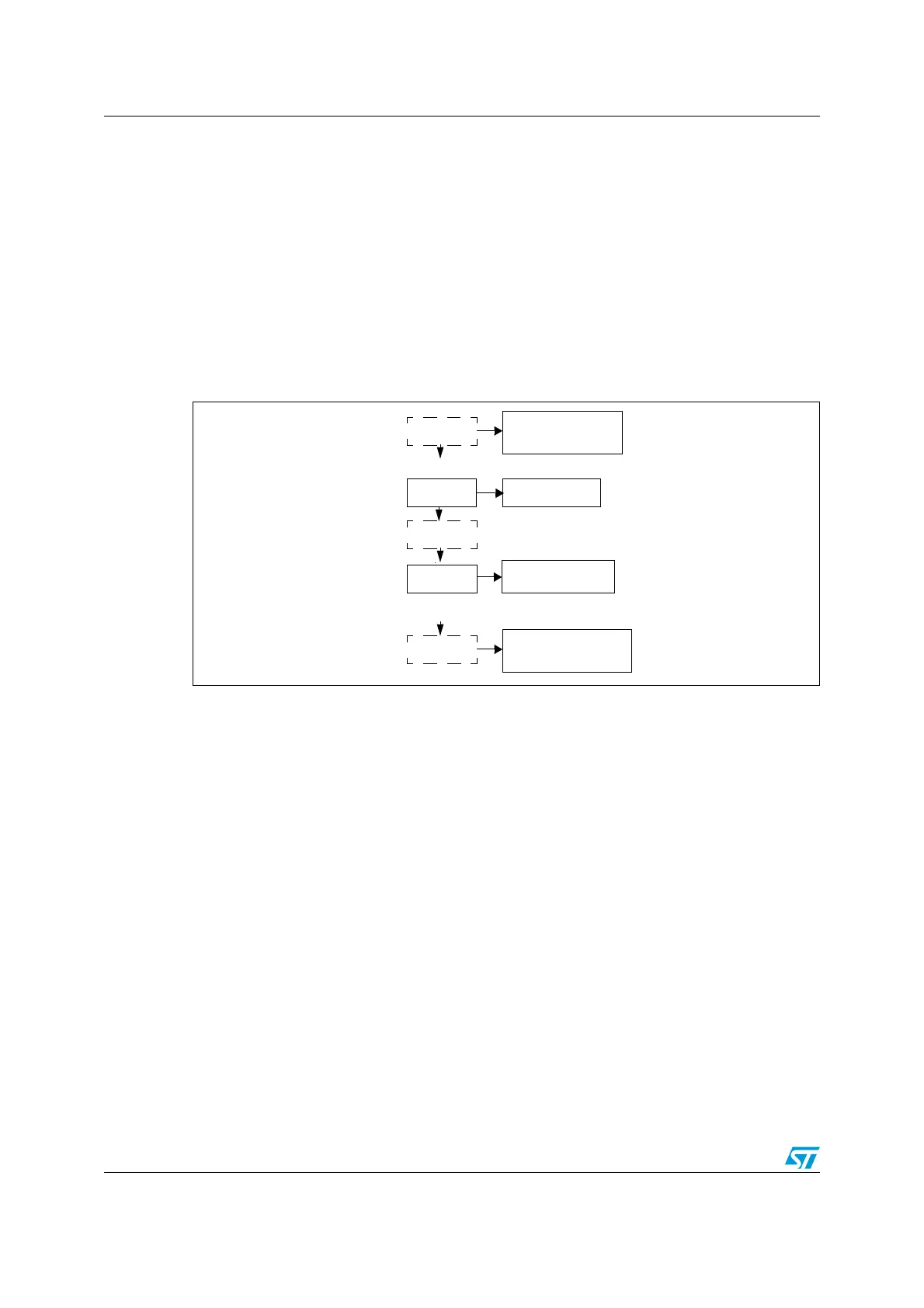

Figure 62. 16-bit read sequence for the TIM1_CCRi register in capture mode

Figure 62 shows the sequence for reading the CCRi registers in the 16-bit timers. This

buffered value remains unchanged until the 16-bit read sequence is completed.

After a complete read sequence, if only the TIM1_CCRiL registers are read, they return the

LS byte of the count value at the time of the read.

If the MS byte is read after the LS byte, it no longer corresponds to the same captured value

as the LS byte.

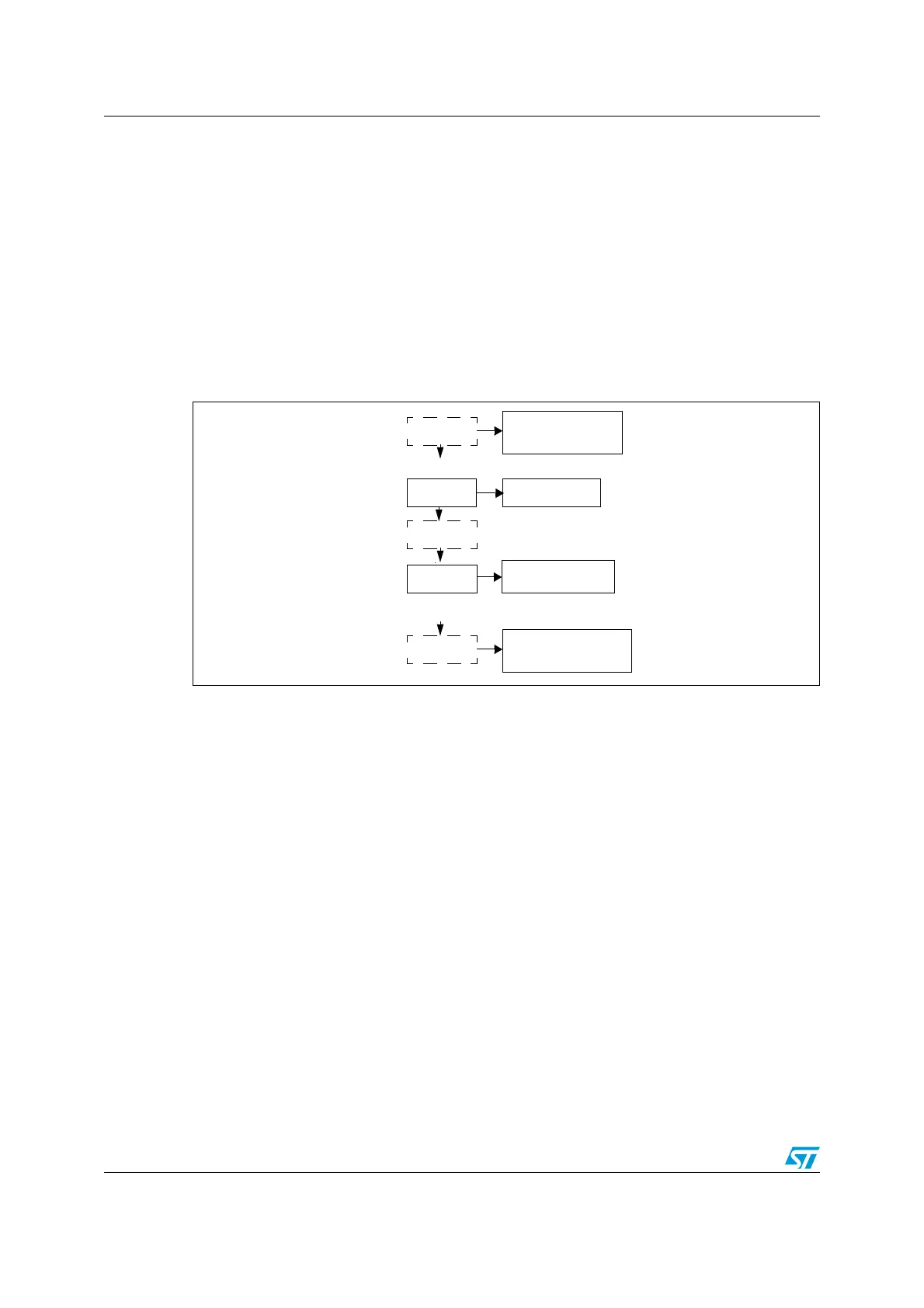

17.5.1 Write sequence for 16-bit TIM1_CCRi registers

16-bit values are loaded in the TIM1_CCRi registers through preload registers. This must

be performed by two write instructions, one for each byte. The MS byte must be written first.

The shadow register update is blocked as soon as the MS byte has been written, and stays

blocked until the LS byte is written. Do not use the LDW instruction, as this writes the LS

byte first, and produces incorrect results in this case.

is frozen

Read

At t0

Read

Preload register

is no longer frozen

At t0 +Δt

Other

instructions

Beginning of the sequence

Sequence completed

Preload register

LS Byte

MS Byte

is buffered into

shadow register

the preload register

Other

instructions

is buffered into

shadow register

the preload register

Other

instructions

Loading...

Loading...