RM0016 Clock control (CLK)

Doc ID 14587 Rev 8 89/449

9.9 CLK register description

9.9.1 Internal clock register (CLK_ICKR)

Address offset: 0x00

Reset value: 0x01

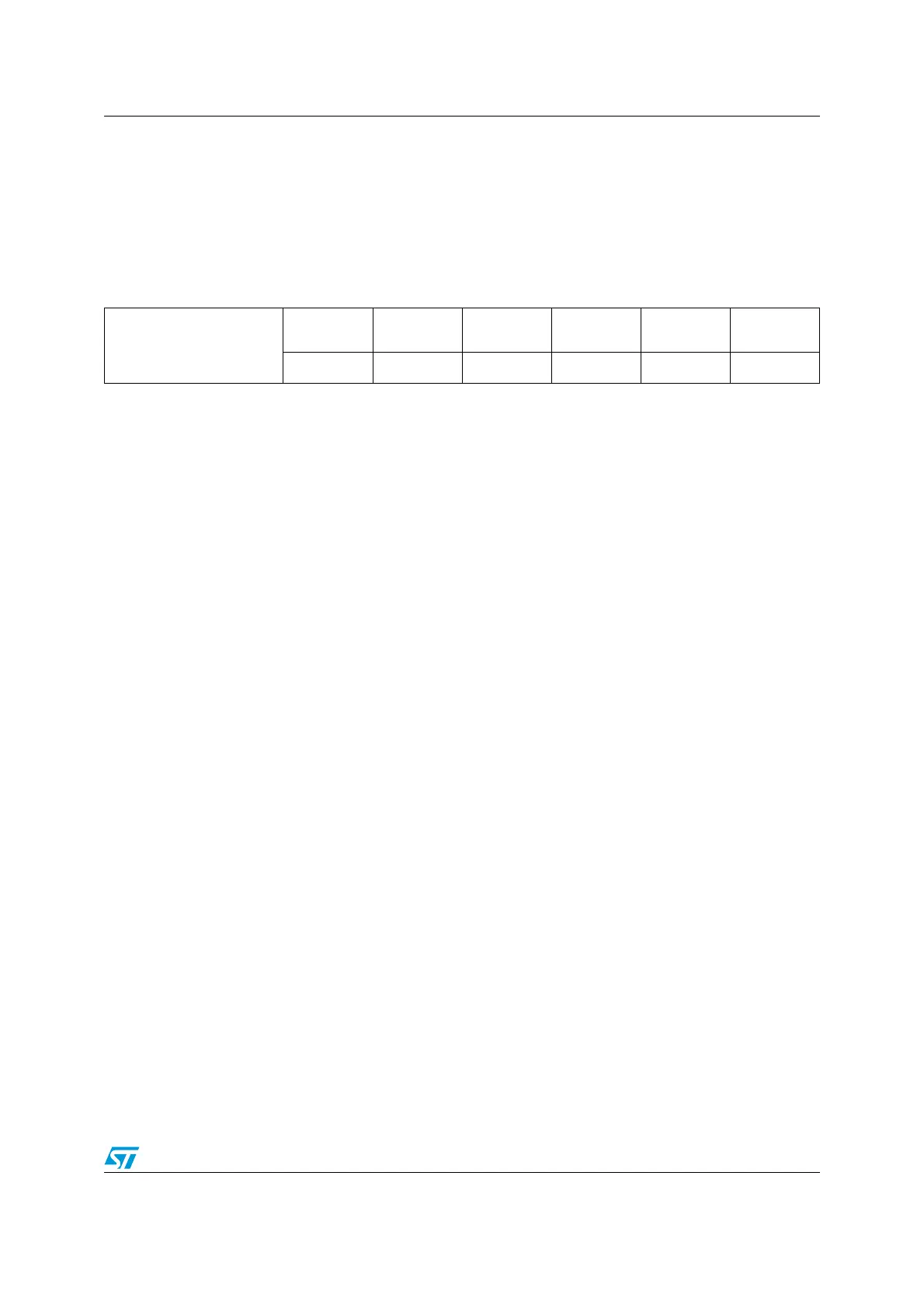

76543210

Reserved

REGAH LSIRDY LSIEN FHW HSIRDY HSIEN

rw r rw rw r rw

Bits 7:6 Reserved, must be kept cleared.

Bit 5 REGAH: Regulator power off in Active-halt mode

This bit is set and cleared by software. When it is set, the main voltage regulator is powered off as

soon as the MCU enters Active-halt mode, so the wakeup time is longer.

0: MVR regulator ON in Active-halt mode

1: MVR regulator OFF in Active-halt mode

Bit 4 LSIRDY: Low speed internal oscillator ready

This bit is set and cleared by hardware.

0: LSI clock not ready

1: LSI clock ready

Bit 3 LSIEN: Low speed internal RC oscillator enable

This bit is set and cleared by software. It is set by hardware whenever the LSI oscillator is required,

for example:

– When switching to the LSI clock (see CLK_SWR register)

– When LSI is selected as the active CCO source (see CLK_CCOR register)

– When BEEP is enabled (BEEPEN bit set in the BEEP_CSR register)

– When LSI measurement is enabled (MSR bit set in the AWU_CSR register)

It cannot be cleared when LSI is selected as master clock source (CLK_CMSR register), as active

CCO source or as clock source for the AWU peripheral or independent Watchdog.

0: Low-speed internal RC off

1: Low-speed internal RC on

Bit 2 FHWU: Fast wakeup from Halt/Active-halt modes

This bit is set and cleared by software.

0: Fast wakeup from Halt/Active-halt modes disabled

1: Fast wakeup from Halt/Active-halt modes enabled

Bit 1 HSIRDY: High speed internal oscillator ready

This bit is set and cleared by hardware.

0: HSI clock not ready

1: HSI clock ready

Loading...

Loading...