RM0016 Serial peripheral interface (SPI)

Doc ID 14587 Rev 8 277/449

20.4.8 SPI Tx CRC register (SPI_TXCRCR)

Address offset: 0x07Reset value: 0x00

20.5 SPI register map and reset values

76543210

TxCRC[7:0]

r

Bits 7:0 TxCRC[7:0]: Tx CRC register

When CRC calculation is enabled, the TxCRC[7:0] bits contain the computed CRC value of the

subsequently transmitted bytes. This register is reset when the CRCEN bit of SPI_CR2 is written to 1.

The CRC is calculated serially using the polynomial programmed in the SPI_CRCPR register.

Note: A read to this register when the BSY flag is set could return a incorrect value

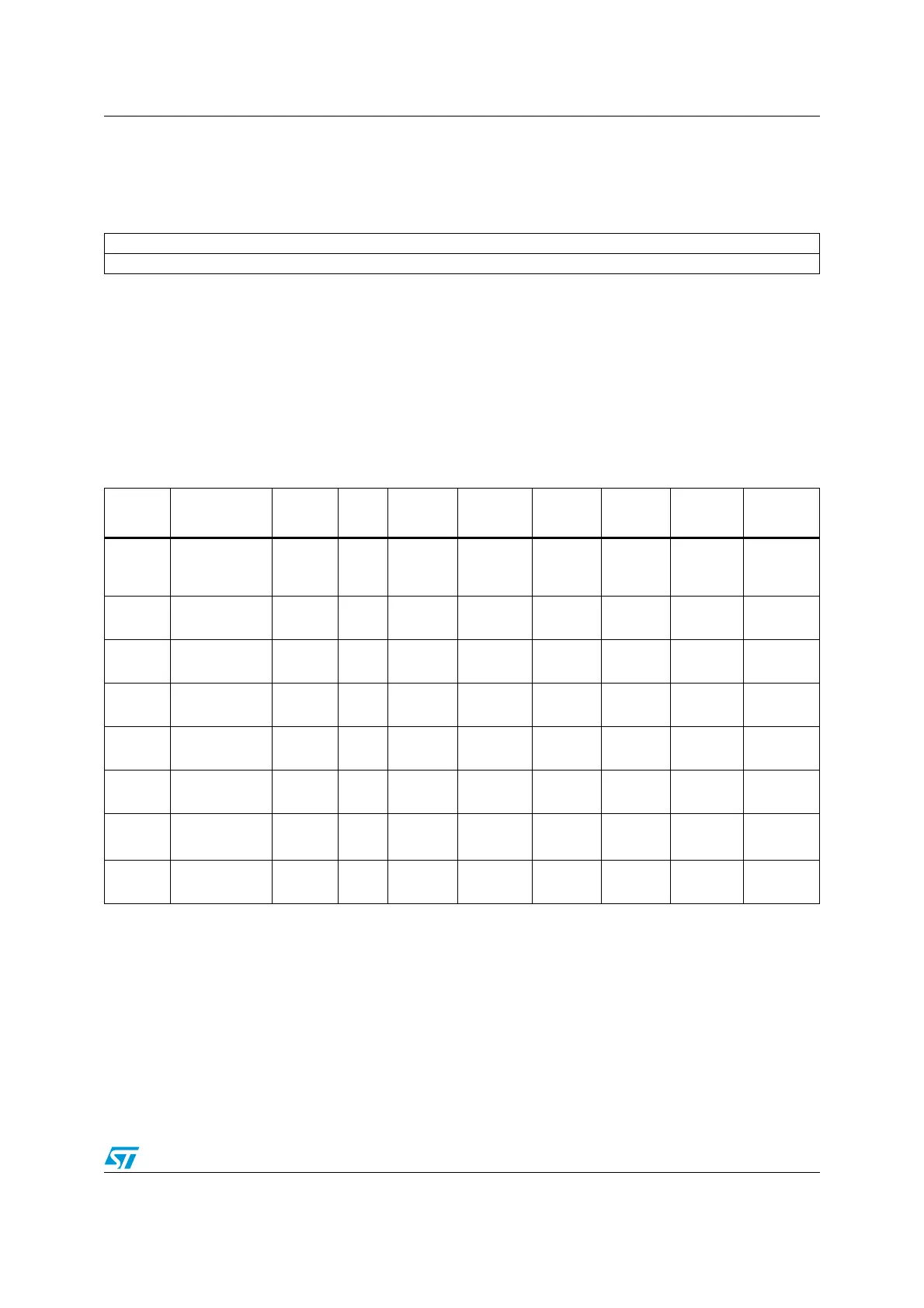

Table 47. SPI register map and reset values

Address

offset

Register

name

76 5 4 3 2 1 0

0x00

SPI_CR1

reset value

LSB

FIRST

0

SPE

0

BR2

0

BR1

0

BR1

0

MSTR

0

CPOL

0

CPHA

0

0x01

SPI_CR2

reset value

BDM

0

BDOE

0

CRCEN

0

CRCNEXT

0

-

0

RXONLY

0

SSM

0

SSI

0

0x02

SPI_ICR

reset value

TXIE

0

RXIE

0

ERRIE

0

WKIE

0

-

0

-

00 0

0x03

SPI_SR

reset value

BSY

0

OVR

0

MODF

0

CRCERR

0

WKUP

0

-

0

TXE

1

RXNE

0

0x04

SPI_DR

reset value

MSB

0

-

0

-

0

-

0

-

0

-

0

-

0

LSB

0

0x05

SPI_CRCPR

reset value

MSB

0

-

0

-

0

-

0

-

0

-

1

-

1

LSB

1

0x06

SPI_RXCRCR

reset value

MSB

0

-

0

-

0

-

0

-

0

-

0

-

0

LSB

0

0x07

SPI_TXCRCR

reset value

MSB

0

-

0

-

0

-

0

-

0

-

0

-

0

LSB

0

Loading...

Loading...