RM0016 16-bit general purpose timers (TIM2, TIM3, TIM5)

Doc ID 14587 Rev 8 217/449

18.3 TIM5 main features

TIM5 features include:

● 16-bit up counting auto-reload counter.

● 4-bit programmable prescaler allowing the counter clock frequency to be divided “on

the fly” by any power of 2 from 1 to 32768.

● 3 independent channels for:

– Input capture

– Output compare

– PWM generation (edge-aligned mode)

– One-pulse mode output

● Synchronization circuit to control the timer with external signals and to interconnect

several timers (See Section 17.4.6 on page 157)

● External trigger input TIM1_ETR (shared with TIM1)

● Interrupt generation on the following events:

– Update: counter overflow, counter initialization (by software)

– Input capture

– Output compare

18.4 TIM2/TIM3/TIM5 functional description

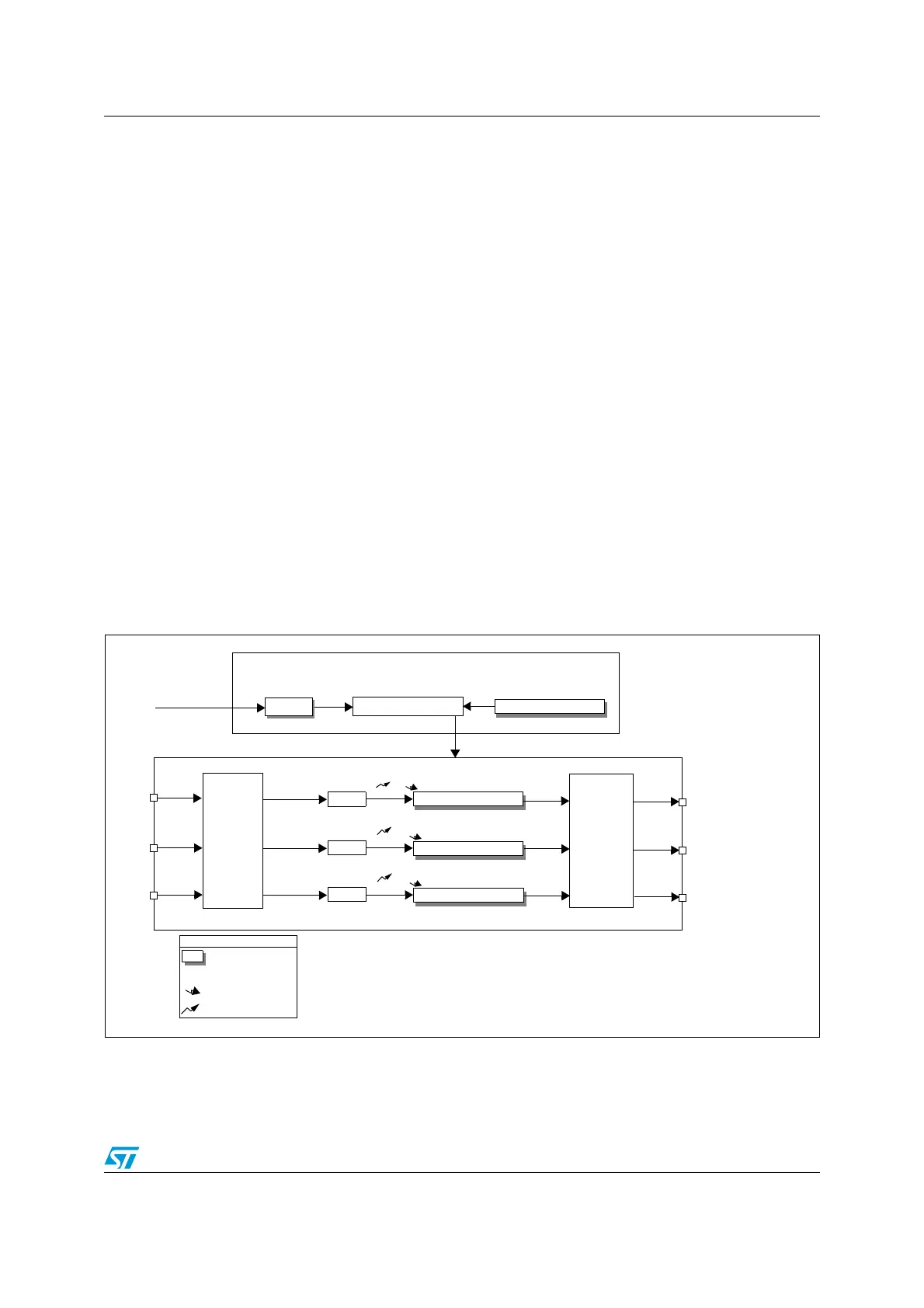

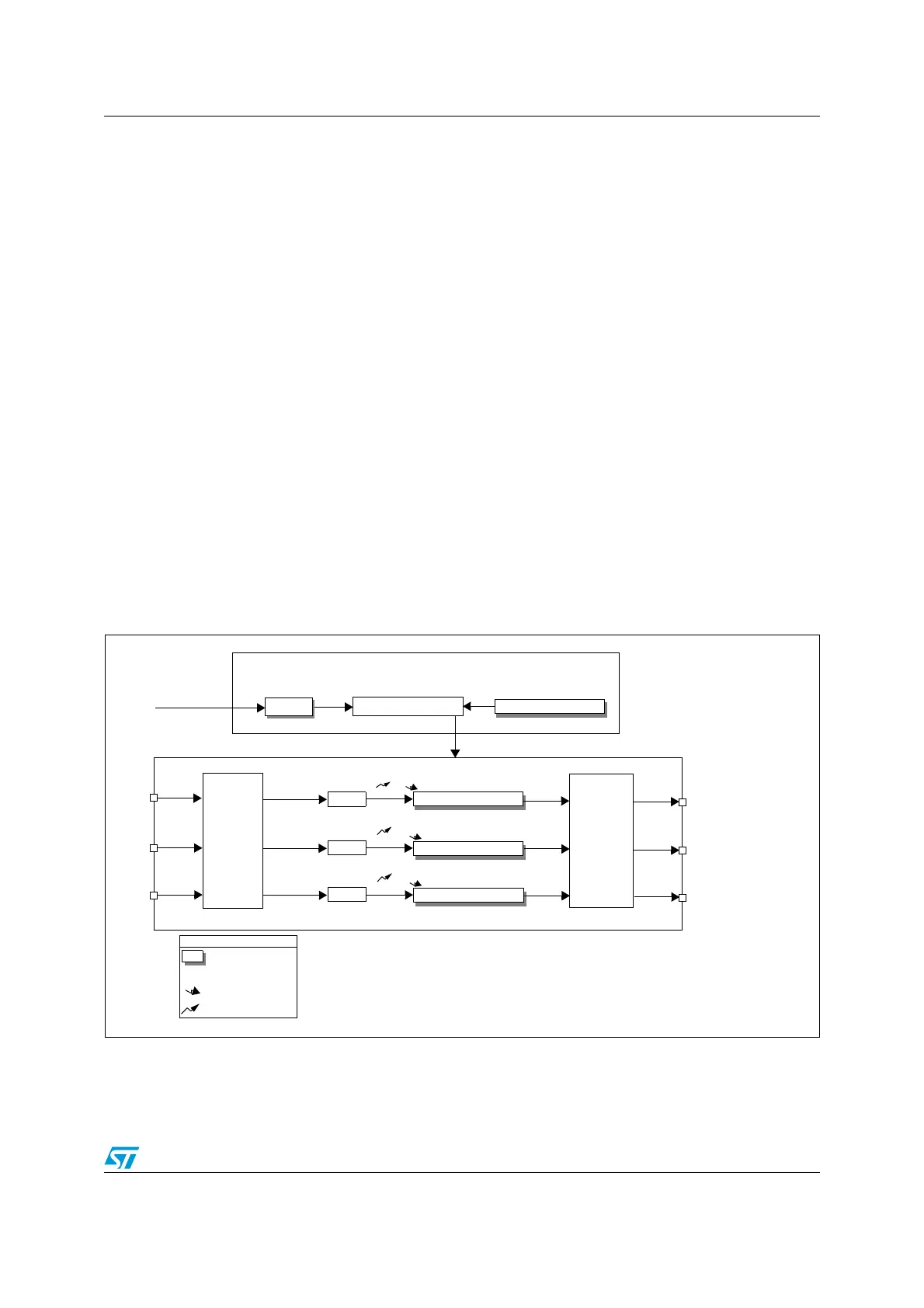

Figure 82. TIM2/TIM3 block diagram

Prescaler

Auto-reload register

UP-DOWN COUNTER

Capture/Compare 1 Register

Capture/Compare 2 Register

UEV

f

MASTER

OC1REF

OC2REF

CK_PSC

IC1

IC2

Prescaler

Prescaler

IC2PS

IC1PS

CC1I

CC2I

TIMx_CH2

OC1

OC2

CK_CNT

UEV

TIME BASE UNIT

INPUT

OUTPUT

CAPTURE COMPARE ARRAY

TI1

TI2

TIMx_CH2

TIMx_CH1

STAGE

STAGE

TIMx_CH1

Reg

event

Legend:

Preload registers transferred

to shadow registers on update

interrupt

event (UEV) according to

control bit

Capture/Compare 3 Register

OC3REF

IC3

Prescaler

IC3PS

CC3I

TIMx_CH3

OC3

UEV

TI3

TIMx_CH3

Loading...

Loading...