RM0016 Controller area network (beCAN)

Doc ID 14587 Rev 8 383/449

SOF = Start Of Frame; ID = Identifier; RTR = Remote Transmission Request; IDE = Identifier Extension;

r0, r1 = Reserved bits; DLC = Data Length Code; CRC = Cyclic Redundancy Code;

Error flag: 6 dominant bits if node is error active else 6 recessive bits.

Suspend transmission: applies to error passive nodes only.

EOF = End of Frame

ACK = Acknowledge bit (send as recessive)

Ctrl = Control

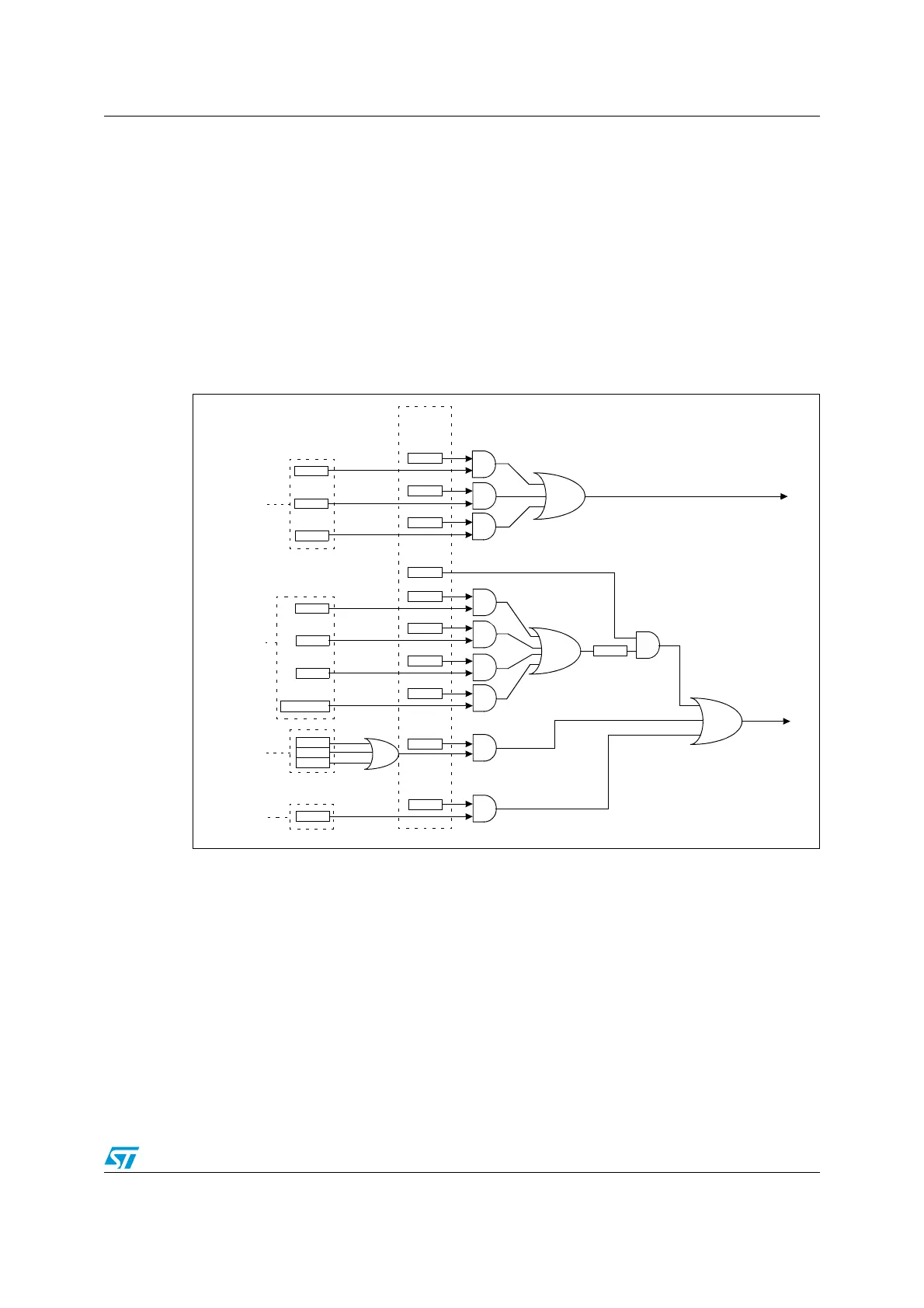

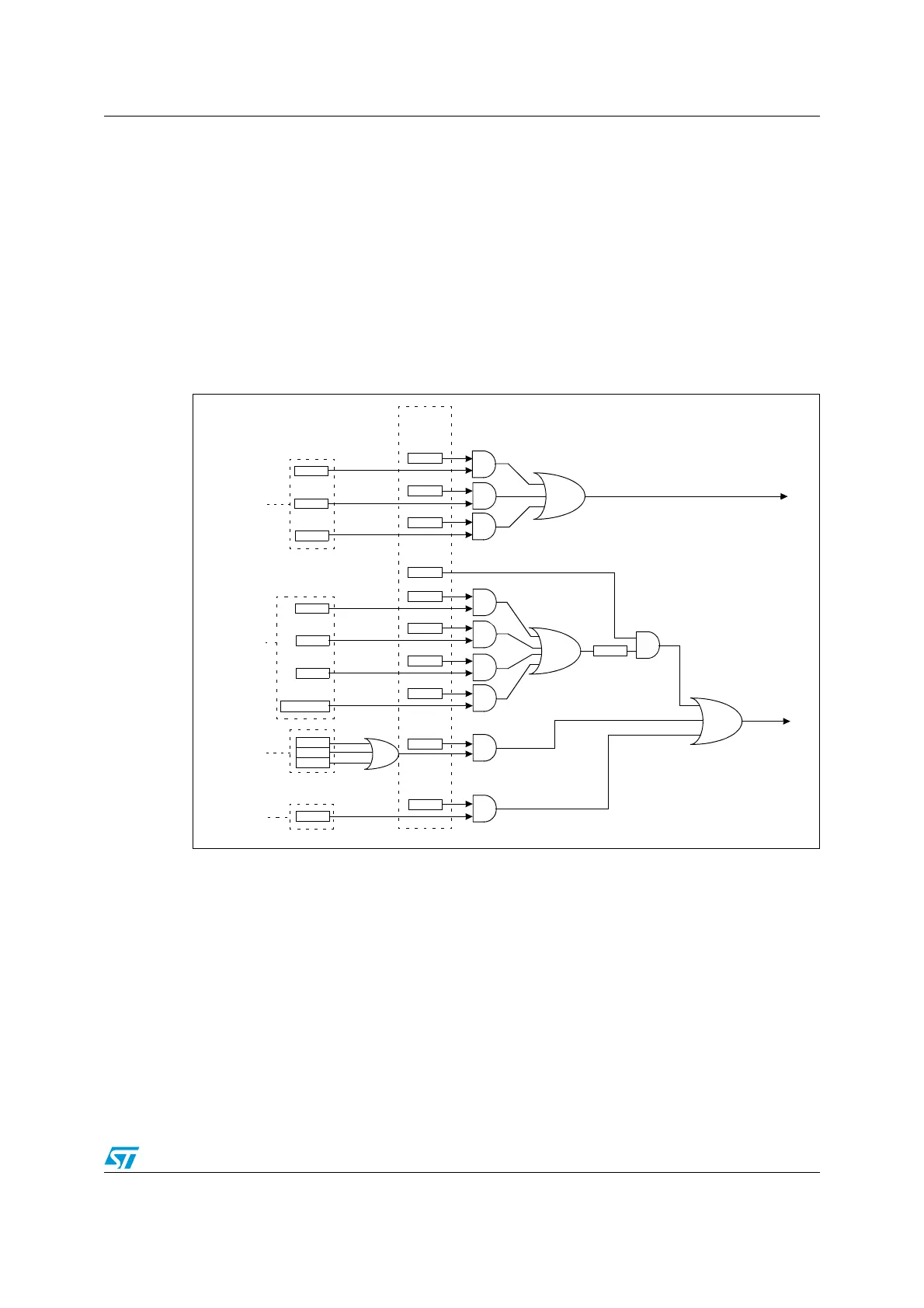

23.7 Interrupts

Two interrupt vectors are dedicated to beCAN. Each interrupt source can be independently

enabled or disabled by means of the CAN Interrupt Enable Register (CAN_IER) and CAN

Error Interrupt Enable register (CAN_EIER).

Figure 155. Event flags and interrupt generation

● The FIFO interrupt can be generated by the following events:

– Reception of a new message, FMP bits in the CAN_RFR register incremented.

– FIFO full condition, FULL bit in the CAN_RFR register set.

– FIFO overrun condition, FOVR bit in the CAN_RFR register set.

● The transmit, error and status change interrupt can be generated by the following

events:

– Transmit mailbox 0 becomes empty, RQCP0 bit in the CAN_TSR register set.

– Transmit mailbox 1 becomes empty, RQCP1 bit in the CAN_TSR register set.

– Transmit mailbox 2 becomes empty, RQCP2 bit in the CAN_TSR register set.

– Error condition, for more details on error conditions please refer to the CAN Error

Status register (CAN_ESR).

– Wakeup condition, SOF monitored on the CAN Rx signal.

RQCP0

RQCP1

CAN_TSR

TMEIE

CAN_IER

TRANSMIT/

EWGF

EWGIE

EPVF

EPVIE

BOFF

BOFIE

1 ℜ≤ LEC ℜ≤

LECIE

CAN_ESR

ERRIE

FMP

FMPIE

FULL

FFIE

FOVR

FOVIE

CAN_RFR

FIFO

INTERRUPT

RQCP2

WKUI

WKUIE

CAN_MSR

INTERRUPT

ERROR

STATUS CHANGE/

ERRI

CAN_MSR

CAN_EIER

Loading...

Loading...