RM0016 Universal asynchronous receiver transmitter (UART)

Doc ID 14587 Rev 8 357/449

22.7.10 Control register 6 (UART_CR6)

Address offset: 0x09

Reset value: 0x00

Note: This register is not available for UART1.

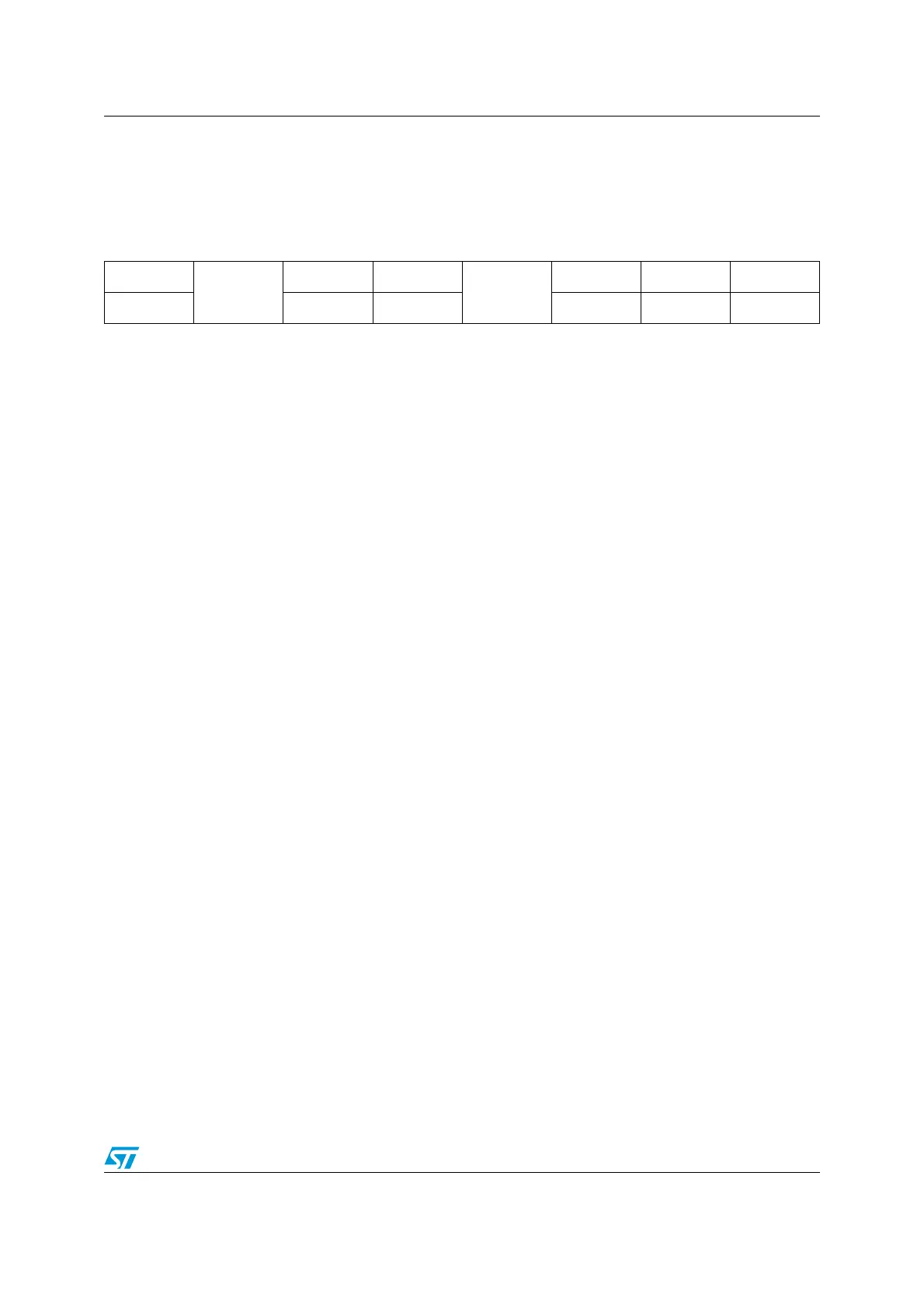

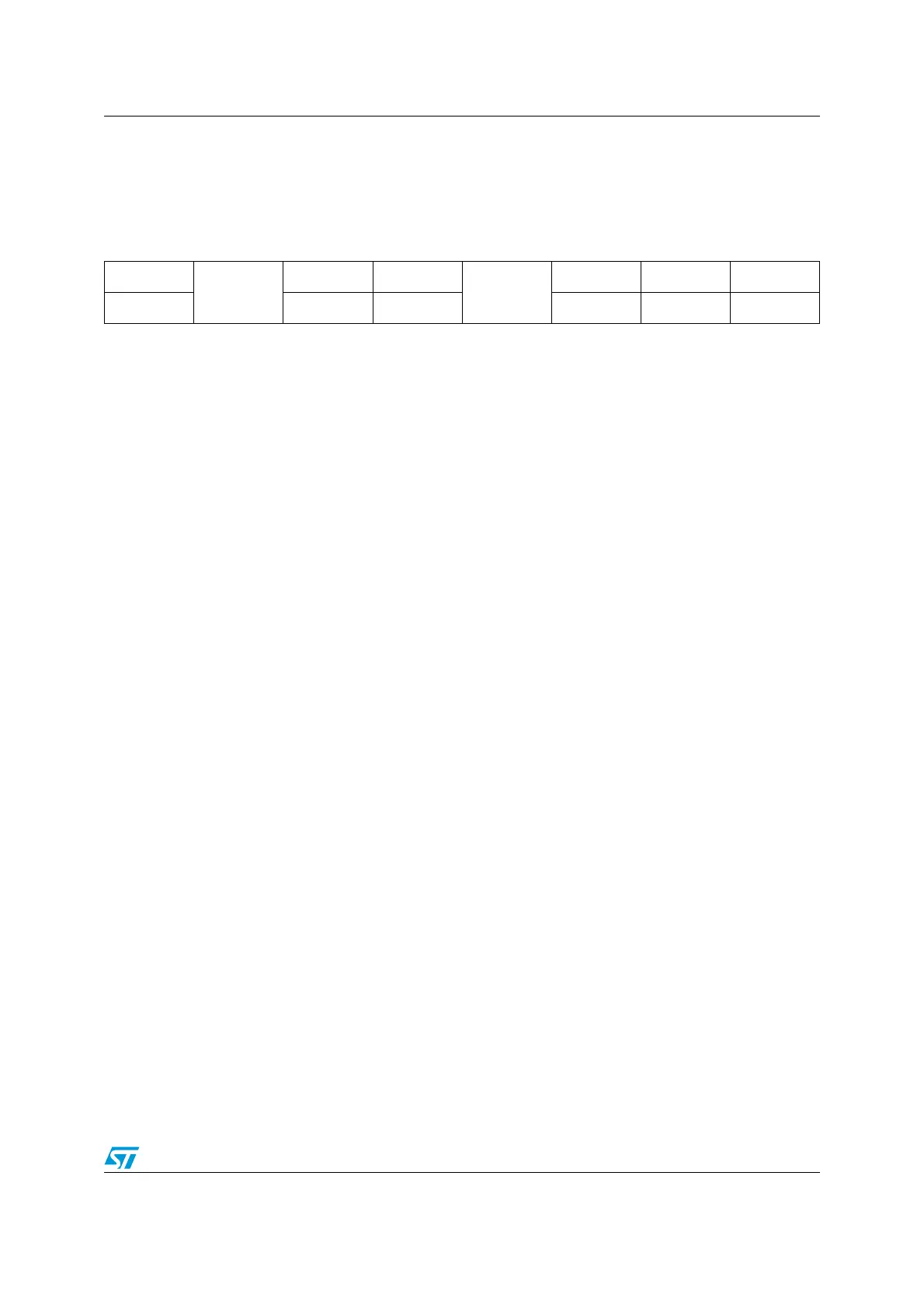

76543210

LDUM

Reserved

LSLV LASE

Reserved

LHDIEN LHDF LSF

rw rw rw rw rc_w0 rc_w0

Bit 7 LDUM: LIN Divider Update Method

0: LDIV is updated as soon as BRR1 is written (if no automatic resynchronization update occurs at

the same time).

1: LDIV is updated at the next received character (when RXNE=1) after a write to the BRR1 register.

LDIV is coded using the two register BRR1 and BRR2

This bit is reset by hardware once LDIV is updated with the measured baud rate at the end of the

synch field.

Bit 6 Reserved

Bit 5 LSLV: LIN Slave Enable

0: LIN Master Mode

1: LIN Slave Mode

Bit 4 LASE: LIN automatic resynchronisation enable

0: LIN automatic resynchronization disabled

1: LIN automatic resynchronization enabled

Bit 3 Reserved

Bit 2 LHDIEN: LIN Header Detection Interrupt Enable.

Header interrupt mask.

0: LIN header detection interrupt disabled

1: LIN header detection interrupt enabled

Bit 1 LHDF: LIN Header Detection Flag.

This bit is set by hardware when a LIN header is detected in LIN slave mode and cleared by software

writing 0.

0: LIN Header not detected

1: LIN Header detected (Break+Sync+Ident)

An interrupt is generated when LHDF=1 if LHDIEN=1

Bits 0 LSF: LIN Sync Field

This bit indicates that the LIN Synch Field is being analyzed. It is only used in LIN Slave mode. In

automatic resynchronization mode (LASE bit=1), when the UART is in the LIN Synch Field State it

waits or counts the falling edges on the RDI line.

It is set by hardware as soon as a LIN Break is detected and cleared by hardware when the LIN

Synch Field analysis is finished. This bit can also be cleared by software writing 0 to exit LIN Synch

State and return to idle mode.

0: The current character is not the LIN Synch Field

1: LIN Synch Field State (LIN Synch Field undergoing analysis)

Loading...

Loading...