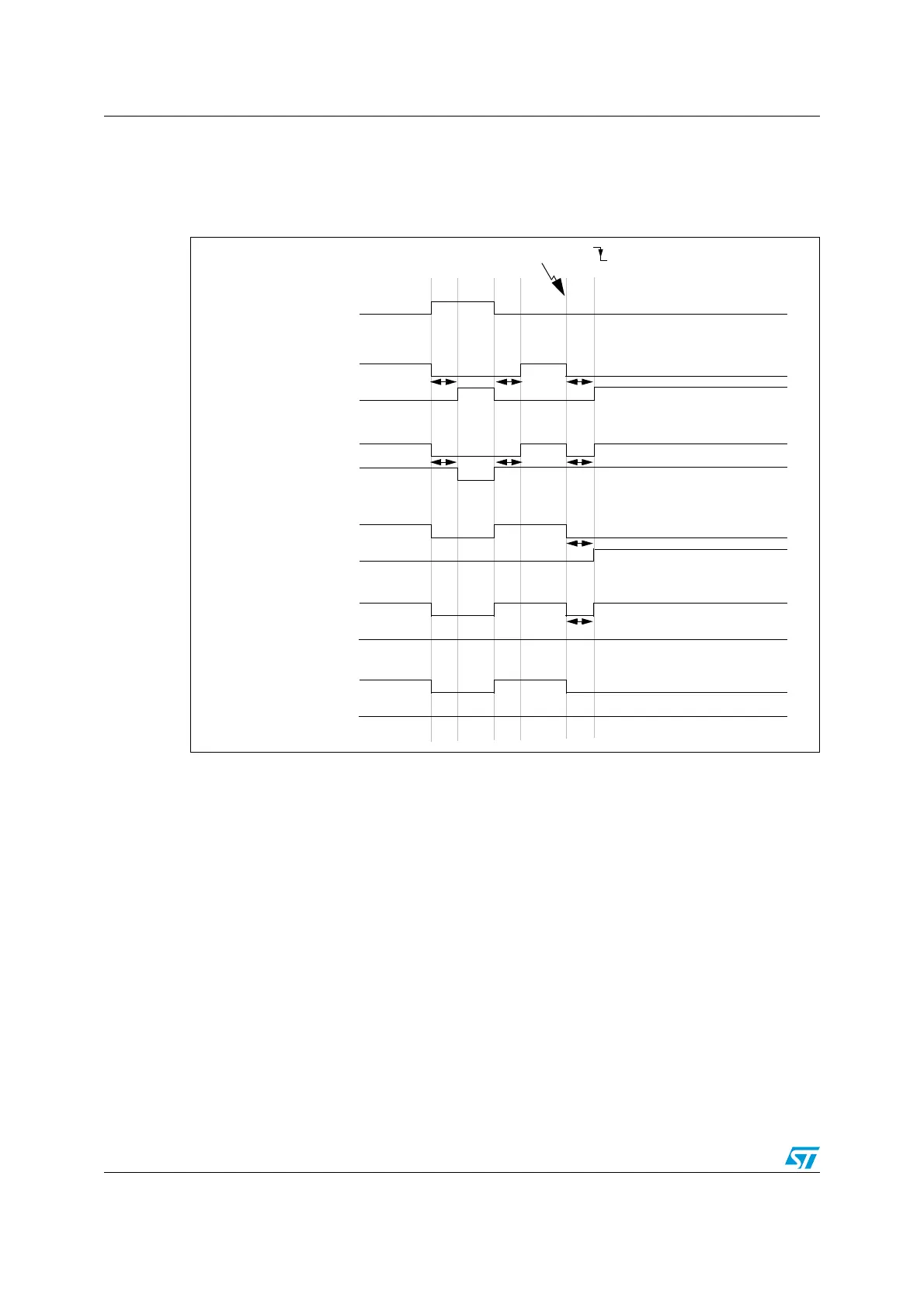

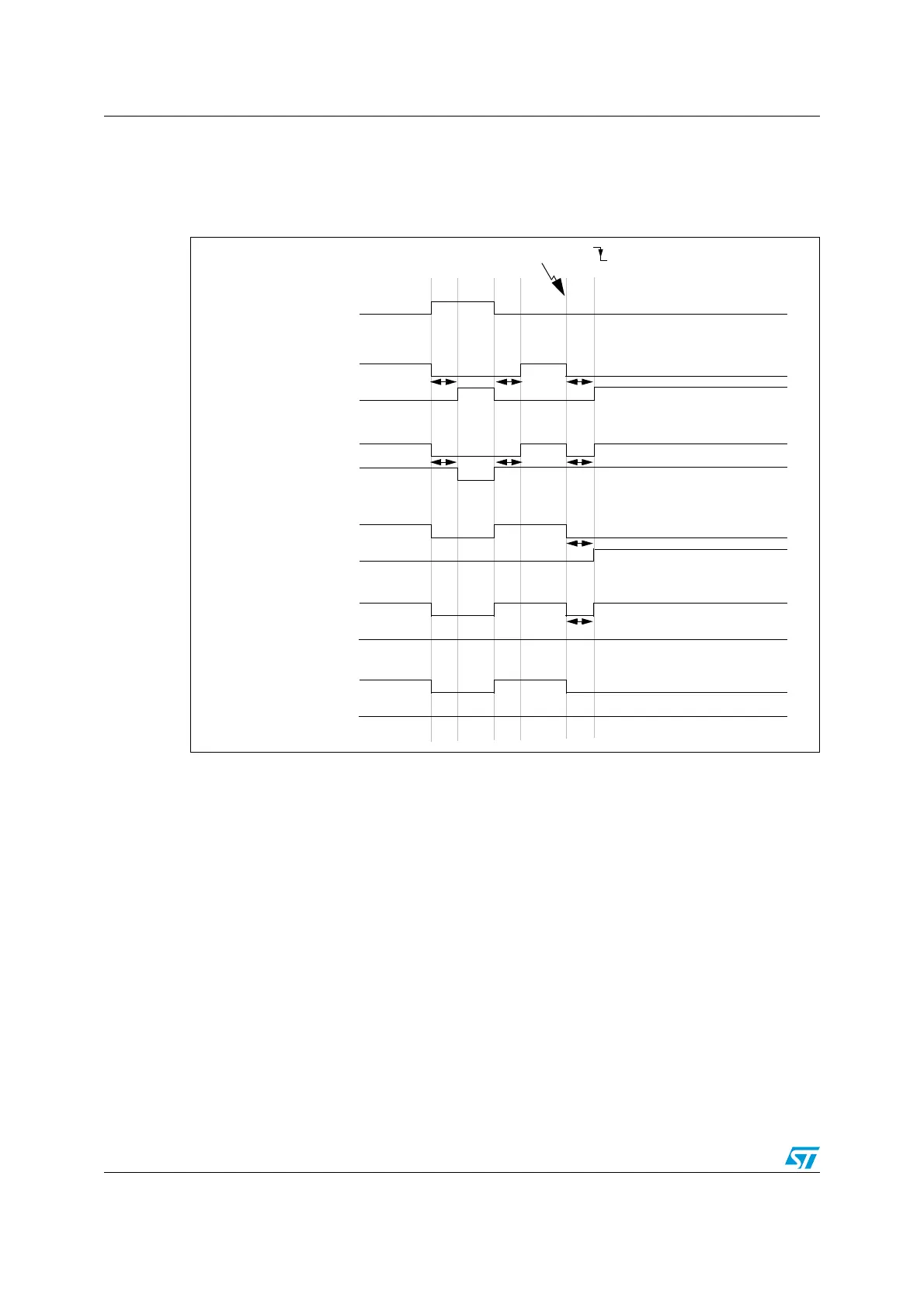

response to a break.

Figure 78. Behavior of outputs in response to a break (TIM1 complementary

delay

BREAK (MOE

OCi

(OCiN not implemented, CCiP=1, OISi=0)

OCi

OCiN

(CCiE=1, CCiP=0, OISi=0, CCiNE=1,

delaydelay

delay

OCi

OCiN

(CCiE=1, CCiP=0, OISi=1, CCiNE=1,

delaydelay

delay

OCi

OCiN

(CCiE=1, CCiP=0, OISi=0, CCiNE=0,

)

delay

OCi

OCiN

(CCiE=1, CCiP=0, OISi=1,

OCi

OCiN

(CCiE=1, CCiP=0, CCiNE=0, CCiNP=0,

CCiNP=0, OISiN=1)

CCiNP=1, OISiN=1)

CCiNP=0, OISiN=1)

CCiNE=0, CCiNP=0, OISiN=0

OISi=OISiN=0 or OISi=OISiN=1)

Loading...

Loading...